Abstract

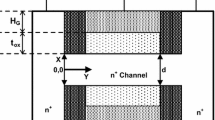

In this paper, an analytical model for junctionless nanotube (JL NT) MOSFET has been developed. The analytical model for minimum central potential, threshold voltage and drain current has been developed by using variable separation method. These model expressions are further applied to analyse the Short Channel Effects (SCEs) of JL NT MOSFET. The electrical performance of proposed device has been investigated by varying different process parameters such as silicon nanotube thickness, gate oxide thickness, and gate length. All the results of developed models have been validated by comparing with so obtained simulated results from genius 3D device simulator of VisualTCAD for different device parameters. JL NT MOSFET with appropriate design parameters can be further explored for circuit applications.

Similar content being viewed by others

References

J.P. Colinge, C.W. Lee, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, A. Kranti, R. Yu. Junctionless transistors: physics and properties, in Semiconductor-on-Insulator Materials for Nanoelectronics Applications (Springer, Berlin, 2011) pp. 187–200

J.P. Colinge, C.W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’neill, A. Blake, M. White, A.M. Kelleher, Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

C.W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, J.P. Colinge, Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94(5), 053511 (2009)

S.J. Choi, D.I. Moon, S. Kim, J.P. Duarte, Y.K. Choi, Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. IEEE Electron Device Lett. 32(2), 125–127 (2010)

S. Gundapaneni, M. Bajaj, R.K. Pandey, K.V. Murali, S. Ganguly, A. Kottantharayil, Effect of band-to-band tunneling on junctionless transistors. IEEE Trans. Electron Devices 59(4), 1023–1029 (2012)

R.T. Doria, M.A. Pavanello, R.D. Trevisoli, M. de Souza, C.W. Lee, I. Ferain, N.D. Akhavan, R. Yan, P. Razavi, R. Yu, A. Kranti, Junctionless multiple-gate transistors for analog applications. IEEE Trans. Electron Devices 58(8), 2511–2519 (2011)

A. Gnudi, S. Reggiani, E. Gnani, G. Baccarani, Semianalytical model of the subthreshold current in short-channel junctionless symmetric double-gate field-effect transistors. IEEE Trans. Electron Devices 60(4), 1342–1348 (2013)

V. Kumari, N. Modi, M. Saxena, M. Gupta, Modeling and simulation of double gate junctionless transistor considering fringing field effects. Solid-State Electron. 107, 20–29 (2015)

G. Hu, P. Xiang, Z. Ding, R. Liu, L. Wang, T.A. Tang, Analytical models for electric potential, threshold voltage, and subthreshold swing of junctionless surrounding-gate transistors. IEEE Trans. Electron Devices 61(3), 688–695 (2014)

T. Holtij, M. Schwarz, A. Kloes, B. Iniguez, Threshold voltage, and 2D potential modeling within short-channel junctionless DG MOSFETs in subthreshold region. Solid-State Electron. 90, 107–115 (2013)

R. Trevisoli, R. Trevisoli Doria, M. de Souza, M. Antonio Pavanello, Analysis of the leakage current in junctionless nanowire transistors. Appl. Phys. Lett. 103(20), 202103 (2013)

K.J. Kuhn, Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59(7), 1813–1828 (2012)

S. Sahay, M.J. Kumar, Diameter dependence of leakage current in nanowire junctionless field effect transistors. IEEE Trans. Electron Devices 64(3), 1330–1335 (2017)

J. Fan, M. Li, X. Xu, Y. Yang, H. Xuan, R. Huang, Insight into gate-induced drain leakage in silicon nanowire transistors. IEEE Trans. Electron Devices 62(1), 213–219 (2014)

J. Hur, B.H. Lee, M.H. Kang, D.C. Ahn, T. Bang, S.B. Jeon, Y.K. Choi, Comprehensive analysis of gate-induced drain leakage in vertically stacked nanowire FETs: inversion-mode versus junctionless mode. IEEE Electron Device Lett. 37(5), 541–544 (2016)

H.M. Fahad, M.M. Hussain, Are nanotube architectures more advantageous than nanowire architectures for field effect transistors? Sci. Rep. 2(1), 1–7 (2012)

D. Tekleab, H.H. Tran, J.W. Sleight, D. Chidambarrao, U.S. Patent No. 8,871,576 (U.S. Patent and Trademark Office, Washington, DC, 2014)

A. Kumar, S. Bhushan, P.K. Tiwari, A threshold voltage model of silicon-nanotube-based ultrathin double gate-all-around (DGAA) MOSFETs incorporating quantum confinement effects. IEEE Trans. Nanotechnol. 16(5), 868–875 (2017)

A. Kumar, S. Bhushan, P.K. Tiwari, Analytical modeling of subthreshold characteristics of ultra-thin double gate-all-around (DGAA) MOSFETs incorporating quantum confinement effects. Superlattices Microstruct. 109, 567–578 (2017)

A. Kumar, S. Bhushan, P.K. Tiwari, Drain current modelling of double gate-all-around (DGAA) MOSFETs. IET Circuits Devices Syst. 13(4), 519–525 (2019)

S. Sahay, M.J. Kumar, Nanotube junctionless FET: proposal, design, and investigation. IEEE Trans. Electron Devices 64(4), 1851–1856 (2017)

S. Rewari, S. Haldar, V. Nath, S.S. Deswal, R.S. Gupta, Numerical modeling of Subthreshold region of junctionless double surrounding gate MOSFET (JLDSG). Superlattices Microstruct. 90, 8–19 (2016)

S. Rewari, V. Nath, S. Haldar, S.S. Deswal, R.S. Gupta, Improved analog and AC performance with increased noise immunity using nanotube junctionless field effect transistor (NJLFET). Appl. Phys. A 122(12), 1049 (2016)

H.M. Fahad, C.E. Smith, J.P. Rojas, M.M. Hussain, Silicon nanotube field effect transistor with core–shell gate stacks for enhanced high-performance operation and area scaling benefits. Nano Lett. 11(10), 4393–4399 (2011)

B. Singh, D. Gola, K. Singh, E. Goel, S. Kumar, S. Jit, Analytical modeling of channel potential and threshold voltage of double-gate junctionless FETs with a vertical Gaussian-like doping profile. IEEE Trans. Electron Devices 63(6), 2299–2305 (2016)

S. Preethi, N.B. Balamurugan, Analytical modeling of surrounding gate junctionless MOSFET using finite differentiation method. Silicon. 1–11 (2020)

C. Jiang, R. Liang, J. Wang, J. Xu, A two-dimensional analytical model for short channel junctionless double-gate MOSFETs. AIP Adv. 5(5), 057122 (2015)

Acknowledgements

Raj Kumar acknowledges the UGC, INDIA for the financial assistance and UIET (ECE), Panjab University, Chandigarh for providing Lab facility.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, R., Bala, S. & Kumar, A. Analytical Modelling and Simulation Analysis of Junctionless Nanotube (JL NT) MOSFET. Trans. Electr. Electron. Mater. 23, 362–370 (2022). https://doi.org/10.1007/s42341-021-00349-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42341-021-00349-6