Abstract

This paper addresses the control design and the experimental validation of a current mode control for a three phase voltage source rectifier. The proposed control law is able to fulfill the voltage regulation and the current tracking control objectives despite of unbalanced and distorted grid voltages. The proposed control law consists of two loops, which are referred as inner tracking loop and the outer voltage regulation loop. The inner loop is designed to provide damping to the system, which also includes and adaptive mechanism. The construction of the current reference is based on the positive component detection of the grid voltage. Therefore, the current produced by the power rectifier is proportional to the fundamental component of the grid voltage, despite of the presence of unbalanced grid voltages. The voltage regulation loop is designed as a proportional-integral controller, which is aimed to regulate the DC output voltage to a desired level. Finally, experimental results are obtained in an experimental prototype of 2 kW to evaluate the performance of the proposed controller.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The increasing use of electronic loads has produced several power quality issues to the utility grid [1]. This kind of loads, also referred as nonlinear loads (NLLs), have negative effects on the power system, for instance, distorted grid currents, low power factor, distorted grid voltage, overheating of electrical machines as well as distribution transformers, among others [2]. Since the power quality is a measure of the efficient use of the electrical energy, this concept has become a critical concern in electrical distribution systems. Thus, several standards like IEC 555-2, IEC 1000-3-2 and IEC 519 [3,4,5] have been developed to maintain safe limits on the harmonic distortion produced and injected by the NLL to the grid. The power electronics equipment involved in a rectification process is commonly related with current harmonic distortion. Examples of these equipments are uncontrolled rectifiers, phase angle controller rectifiers among others, which produce highly distorted grid currents. As a solution, power converters with capacity of power factor corrector (PFC) have been developed [6, 7]. This kind of power converters are able to mitigate the harmonic pollution and thus, achieve a power factor close to unity.

The idea behind of the PFC based on pulse-width modulation (PWM) rectifier is to select an adequate power converter and design a proper control law aimed to regulate the DC output towards a desired reference keeping a power factor close to the unity. The later means that the control law is able to track a desired line current reference, which is constructed free of harmonic distortion and in phase with the grid voltage. In this sense, several control approaches have been proposed for voltage source rectifiers to deal with the harmonic pollution problem. For example, in [8,9,10] direct power control (DPC) approach is applied to reduce the harmonic content by providing a sinusoidal line current. In this technique, the real and reactive powers are used to generate the modulating signals for the power devices. In [11] and [12], model predictive control (MPC) is used to improve the DPC technique. In [13], virtual-flux-based approach is applied to enhance DPC strategy. The current mode control (CMC) approach is focused on solving the current tracking problem, that is, the line current is forced to track a desired current reference. Several strategies have been developed following the CMC. For instance, in [14] a current control strategy to deal with the offset in measurement error and input voltage is proposed. This control strategy is designed in the synchronous reference frame, therefore, the resulting control scheme is designed as two PI vector controllers. In [15], sliding mode control is applied to improve the CMC technique. In recent years AC-DC conversion has been used in smart grid applications due to the need of a power factor close to unity [16,17,18]. In [19] the smart grid approach is presented as a solution to grid power quality problems by using several power conversion techniques where the DC-DC stage is used to provide power conditioning the DC-DC stage. Another application of voltage source rectifers (VSRs) is in high voltage direct current (HVDC) transmission systems. For instance, in [20] the VSR is used as a stage of a back-to-back converter. In this case, VSR is used to control the DC-link voltage and reactive power, and acts as an interface between the converter and the AC source.

Besides harmonic distortion, the voltage unbalance is one of the most common power quality disturbances in industrial systems. The voltage unbalance frequently occurs due to unsymmetrical impedances of transmission and distribution lines, unequal distribution of single-phase loads, unbalanced three-phase loads, faulty delta transformer connections and single-phase-to-ground faults, among others. Most of the electric equipment have damage susceptibility under unbalance voltage conditions. For instance, operation of induction motors at \(5\%\) of voltage unbalance factor (VUF) is not recommended [21, 22]. Additionally, three-phase uncontrolled rectifiers with large output capacitive filters are seriously affected by voltage unbalance. This class of rectifiers produce an unbalance current factor of \(100\%\) with only a \(0.3\%\) of VUF. It has been also previously reported that \(0.3\%\) of VUF in three-phase uncontrolled rectifiers causes non-characteristics harmonics. In this case, third harmonic currents as large as \(19.2\%\) of magnitude may appear. As a consequence, several international standards have a restriction on the unbalance factor, such as the IEC 61000-2-2 which limits the VUF to be less than \(2\%\) [23]. Important efforts have also been done to propose advanced control strategies for PFCs based on PWM rectifiers which must be able to maintain an adequate system performance despite of input voltage unbalance conditions. In [24], active power oscillation cancelation methods used to enhance the DPC technique, are presented. It was shown that the controller was able to deal with input unbalance voltages. In [25], a new definition of the reactive power is presented for a DPC technique which is aimed to deal with the input voltage unbalance, and does not require the estimation of positive and negative sequences of the grid. In [26], an improved dead-beat based control for a three-phase PWM rectifier under harmonic and unbalance disturbances is presented. In [27], a control scheme for a voltage source converter (VSC) under input voltage disturbances is presented. This scheme is based on a sinusoidal disturbance estimation, and is aimed to model the voltage unbalance as a disturbance, which is estimated and used in a feedback control.

In this paper, the experimental validation and controller design of a three-phase PFC based on a VSR PWM rectifier under unbalance and distorted grid voltages are presented. The proposed control law is designed directly in \(\alpha \beta\) coordinates avoiding extra transformation as occurs in DPC techniques. The construction of an adequate current reference is essential in the proposed control design, where the positive component of the grid voltage is used for this purpose. The current reference results in a signal proportional to the positive component of the grid voltage despite of grid voltage unbalance and grid voltage harmonic distortion. To obtain the positive component of the grid the guidelines presented in [8] and [9] have been considered. The proposal of the controller considers the decoupling assumption, which establishes that the faster dynamics can be decoupled from the slower dynamics, that is, the dynamics of the current decoupled from the capacitor voltage dynamics. Therefore the controller can be splitted in two main loops, namely, current tracking loop and voltage regulation loop. The first is formed by a proportional gain plus a couple of adaptive estimators, which are capable to deal with the parameter uncertainties of the input filter. The purpose of the current loop is to track a desired current reference constructed by using the estimation of the positive component of the grid voltage, this allows to obtain a sinusoidal line current despite the slight amount of harmonic pollution and the unbalanced operation of the grid voltage. Also, the inner loop is designed including a feedforward term since the system model considers the grid impedance. This term is added to deal with the grid impedance effects since it acts as a decoupling term. The voltage regulation loop consists of a proportional-integral (PI) controller which guarantees the regulation of the DC voltage to a constant reference. The output of the voltage loop is used to construct the current reference together with the estimation of the positive component of the grid voltage. The PI controller includes a low pass filter (LPF), that allows restricting the bandwidth and avoids the harmonic pollution in the current reference produced by the rectification process.

The rest of the paper is organized as follows. In Section 2, the model of the VSR is presented. In Section 3, the design of the proposed controller is presented. In Section 4, experimental results, in a 2 kW prototype, are presented including unbalanced and distorted grid voltage conditions. Finally, in Section 5, the conclusions of the paper are presented.

2 System description

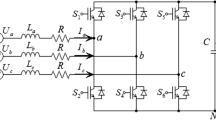

In Fig. 1, the representation of a full bridge three-phase VSR topology is shown. As it can be observed, the rectifier is connected at the point of common coupling (PCC) into the grid through an inductive filter. This converter is used as PFC due to its capability to achieve a power factor close to unity. The dynamics of the rectifier as PFC is described by the average model,

where \(\varvec{i}_{S,\alpha \beta }=[i_{S\alpha },i_{S\beta }]^\top\), \(\varvec{v}_{\alpha \beta }=[v_{\alpha },v_{\beta }]^\top\) and \(\varvec{u}_{\alpha \beta }=[u_\alpha ,u_\beta ]^{\top }\) are the currents flowing through the grid impedance, the voltages at the PCC and the duty cycles, respectively, all in \(\alpha \beta\) reference frame. Notice that, \(\varvec{v}_{\alpha \beta }=\varvec{v}_{G,\alpha \beta }-L_G{\dot{\overline{\varvec{i}}}}_{S,\alpha \beta }-R_G\varvec{i}_{S,\alpha \beta }\) represents the voltage between the PCC and the neutral point, which includes the impedance of the grid. The signal \(\varvec{e}_{\alpha \beta }:=(v_{C0}\varvec{u}_{\alpha \beta })/2\) is the control input; \(v_{C0}\) is the DC voltage in the capactior; \(L_S\), \(R_S\), C and R are the inductance of the input filter, the parasitic resistor of the input filter, the output capacitance and the load resistor, respectively. In order to obtain the average model of the VSR, the switching vector \([\rho _1,\rho _2,\rho _3]^{\top }\) is substituted in the dynamics equations by the respective duty cycles vector \([u_1,u_2,u_3]^{\top }\). Note that, in this paper, bold typeface characters denote either vectors or matrices and normal typeface characters depict scalar quantities. The Clarke’s transformation is used to transform \(\varvec{\nu }_{123}\) to \(\varvec{\nu }_{\alpha \beta }\),

2.1 Grid voltage model under unbalanced condition and positive component estimation

In order to simplify presentation, the assumption is made that the grid voltage is considered without any harmonic pollution, then the model under balanced and unbalanced conditions is obtained. The grid voltage can be considered formed by positive- and negative-components, whose fundamental frequency is \(f=\omega /2 {\pi }\). A mathematical description of the grid voltage under unbalanced operation in \(\alpha \beta\) reference frame is obtained by means of the method presented in [8] as follows.

where \(\varvec{v}_{\alpha \beta ,p}\) and \(\varvec{v}_{\alpha \beta ,n}\) represent the positive and negative symmetrical components of the grid voltage \(\varvec{v}_{\alpha \beta }\); \(\sigma _0\) represents the phase angle; \(\varvec{V}_{dq}^+={\left[ V_d^+, V_q^+\right] }^{\top }\) and \(\varvec{V}_{dq}^-={\left[ V_d^-,V_q^-\right] }^{\top }\) are vectors of harmonic coefficients. Next, the guidelines shown in [8] and [28] are applied to obtain the positive component of the grid voltage. From (4), the model of the grid voltage in unbalanced operation is expressed as:

It is important to note that the term \({\varvec{\varphi }}_{\alpha \beta }\) is defined as \(\varvec{\varphi }_{\alpha \beta }:=\varvec{v}_{\alpha \beta ,p}-\varvec{v}_{\alpha \beta ,n}\), which completes the model of the voltage of the grid in unbalanced operation. Observe that, in balanced condition, the model of \(\varvec{v}_{\alpha \beta }\) can be simplified to \(\dot{\varvec{v}}_{\alpha \beta }=\varvec{J}\omega \varvec{v}_{\alpha \beta }\), and \(\varvec{\varphi }_{\alpha \beta }=\varvec{v}_{\alpha \beta }\). Considering (4) and the definition of the complementary term \({\varvec{\phi }}_{\alpha \beta }\), the following relationship is established,

where \(\varvec{I}\) is the \(2\times2\) identity matrix. Next, from (7) \(\varvec{v}_{\alpha \beta ,p}\) and \(\varvec{v}_{\alpha \beta ,n}\) are obtained as a linear combination of \(\varvec{v}_{\alpha \beta }\) and \(\varvec{\varphi }_{\alpha \beta }\), this leads to

The term \(\varvec{v}_{\alpha \beta ,p}\) is the fundamental signal used to generate the current reference for the current tracking loop. As will be observed later, the positive component of \(\varvec{v}_{\alpha \beta }\) is obtained from (8). Observe that, \(\varvec{v}_{\alpha \beta ,p}\) is produced by a linear combination, which is dependent of \(\varvec{\varphi }_{\alpha \beta }\) and \(\varvec{v}_{\alpha \beta }\). Nonetheless, the term \(\varvec{\varphi }_{\alpha \beta }\) is unavailable for measurement. Hence, to deal with this inconvenience, auxiliary estimators of \(\varvec{v}_{\alpha \beta ,p}\) and \(\varvec{\varphi }_{\alpha \beta }\) are proposed. By adding a damping term to the system model (5)–(6), the following structure for the estimators is obtained,

where \(\tilde{\varvec{v}}_{\alpha \beta }:=\varvec{v}_{\alpha \beta }-\hat{\varvec{v}}_{\alpha \beta }\); \(\varsigma\) is a positive design term, which provides damping. Observe that, by estimating the signals \(\hat{\varvec{v}}_{\alpha \beta }\) and \(\hat{\varvec{\varphi }}_{\alpha \beta }\) through the use of the proposed estimator, (9)–(10), the positive component of the grid voltage is calculated as \(\hat{\varvec{v}}_{\alpha \beta ,p}=(\hat{\varvec{v}}_{\alpha \beta }+\hat{\varvec{\varphi }}_{\alpha \beta })/2\).

2.2 Control objectives

The main purpose of a three-phase VSR performing as PFC is to achieve a power factor close to unity, that is, to compensate the harmonic distortion and provide a sinusoidal line current in phase with the grid voltage and also supply a regulated DC voltage to the load. To ease the controller design, a time-scale separation is assumed between the faster current, and the slower DC capacitor voltage dynamics, this is also known as decoupling assumption. This provides the possibility to separate the design of the controller in two main loops, namely, current tracking loop and voltage regulation loop [29]. Before starting the design of the controller, these control objectives for the three-phase VSR must be formally expressed as follows:

-

1)

Current tracking control objective

The current of the grid must track a current reference signal \(\varvec{i}_{S,\alpha \beta }\) in order to achieve a power factor close to unity, that is,

The current reference signal can be calculated as a signal proportional to the positive component of the grid voltage \(\varvec{v}_{\alpha \beta ,p}\), that is,

where \(\varvec{i}_{S,\alpha \beta }^*\) represents the current reference; \(P^*\) is a scalar representing the power reference, which is calculated at the voltage regulation loop. Observe that, the term \(\Vert \varvec{v}_{\alpha \beta ,p}\Vert ^2\) represents the root-mean-square (RMS) value of \(\varvec{v}_{\alpha \beta ,p}\).

-

2)

Voltage regulation control objective

The voltage of the capacitor must be regulated towards a desired constant reference \(V_{ref}\), that is,

This guarantees that a regulated DC voltage is delivered to the load. Fulfilment of this objective yields an output signal, from the voltage regulation loop, that together with \(\hat{\varvec{v}}_{\alpha \beta ,p}\) is used to construct the current reference.

3 Controller design

In this section, the controller of the VSR based on positive component estimation is presented. The controller consists in two main loops, namely, current tracking loop to allow a proper tracking of the current reference constructed by using the estimate of the positive component of the grid voltage, and a voltage regulation loop, which achieves the delivery of a properly regulated DC capacitor voltage to the load. The following equations provide a more complete model than system (1)–(3) since it includes the grid impedance modeling.

3.1 Current tracking loop

To design the current control loop, only the subsystem (12) is considered which represents the dynamics of the grid current. First of all, the current dynamics (12) is expressed in terms of its increments as:

It can be observed that, the current reference derivative \(\dot{\bar{\varvec{i}}}_{S,\alpha \beta }^*\) can be approximated as \(\dot{\bar{\varvec{i}}}_{S,\alpha \beta }^*=P^*\dot{\hat{\varvec{v}}}_{\alpha \beta ,p}/\Vert \varvec{v}_{\alpha \beta ,p}\Vert ^2\), where the term \(\dot{\hat{\varvec{v}}}_{\alpha \beta ,p}\) is obtained as:

Therefore, the derivative of the current reference is obtained in terms of the current reference as \(\dot{\bar{\varvec{i}}}_{S,\alpha \beta }^*=\omega \varvec{J}\varvec{i}_{S,\alpha \beta }^*\) and with this, the error model of the system can be established as:

In order to provide a stable current tracking and taking into account the structure of the system (16) a controller can be proposed as,

where \(\tilde{\varvec{i}}_{S,\alpha \beta }:=\varvec{i}_{S,\alpha \beta }-\varvec{i}_{S,\alpha \beta }^*\) and \(\varvec{K}_i = \hbox {diag}\{k_{i\alpha },k_{i\beta }\}\) is a design positive definite matrix. Due to the impossibility of taking measurements of the terms \(R_S\varvec{i}_{S,\alpha \beta }^*\) and \(L_S\omega \varvec{J}\varvec{i}_{S,\alpha \beta }^*\), a couple of estimators of the parameters \(\hat{R}_S\) and \(\hat{L}_S\) are proposed. Observe that, the current reference is computed by making use of the output of the voltage regulation loop and \(\varvec{v}_{\alpha \beta ,p}\). Hence, it is possible to express without loss of generality the controller as follows

The design of the estimations \(\hat{R}_S\) and \(\hat{L}_S\) is performed following the adaptive scheme described next. The closed loop subsystem (16) and controller (17) yields the following perturbed LTI system,

which is known as the error dynamics. Where the terms \(\tilde{L}_S:=\hat{L}_S-L_S\), \(\tilde{R}_S:=\hat{R}_S-R_S\) and the term \(\varvec{K}:=\varvec{K}_i+R_S\varvec{I}\), thus, the term K is of the form \(\varvec{K}={\text {diag}}\{{k}_{\alpha }, {k}_{\beta }\}\). It can be observed that the terms \(R_S\) and \(\varvec{K}_i\), which are present on the current error signal \(\varvec{i}_{S,\alpha \beta }\), are damping terms, where \(R_S\) is an unknown positive constant and \(\varvec{K}_i\) is a diagonal matrix that has positive control design parameters at its diagonal.

The design of the adaptive law follows the Lyapunov guidelines, where the following energy storage function is proposed:

The time derivative of the Lyapunov function \(\dot{W}\) along the trajectories of (18) is given by

which is forced to be negative semidefinite by compelling the estimates \(\hat{R}_S\) and \(\hat{L}_S\) satisfy the following dynamics,

where \(\eta _{Rs}>0\) and \(\eta _{Ls}>0\), are design parameters representing the adaptive gains. Therefore

As W is radially unbounded and \(\dot{W}\) is negative semi-definite then \(\tilde{i}_{S,\alpha }\in \mathcal {L}_2\bigcap \mathcal {L}_\infty\), \(\tilde{i}_{S,\beta }\in \mathcal {L}_2\bigcap \mathcal {L}_\infty\), \(\tilde{R}_S\in \mathcal {L}_\infty\) and \(\tilde{L}_S\in \mathcal {L}_\infty\). Assuming that \(i_{S,\alpha }^*\) and \(i_{S,\beta }^*\) are bounded, then \(\dot{\tilde{i}}_{S,\alpha }\in \mathcal {L}_\infty\) and \(\dot{\tilde{i}}_{S,\beta }\in \mathcal {L}_\infty\), and thus, \(\tilde{i}_{S,\alpha }\rightarrow 0\) and \(\tilde{i}_{S,\beta }\rightarrow 0\), asymptotically. Moreover, \(\dot{W}\equiv 0\) implies \(\tilde{i}_{S,\alpha }\equiv 0\), \(\tilde{i}_{S,\beta }\equiv 0\), \(\dot{\tilde{i}}_{S,\alpha }\equiv 0\), \(\dot{\tilde{i}}_{S,\beta }\equiv 0\), \(i_{S,\alpha }=i_{S,\alpha }^*\) and \(i_{S,\beta }=i_{S,\beta }^*\), then from (18) the only solution for the estimation errors is \(\tilde{R}_S=0\) and \(\tilde{L}_S=0\), and thus, the estimates converge towards the right values asymptotically, i.e., \(\hat{R}_S\rightarrow R_S\), \(\hat{L}_S\rightarrow L_S\) as \(t\rightarrow \infty\).

Remark 1:

Notice that the introduction of the feedforward term \(\varvec{v}_{\alpha \beta }\) in controller (17) causes the decoupling of the line impedance dynamics. That is, the terms associated with this impedance are eliminated from the error dynamics (18).

3.2 Voltage regulation loop

The design of the voltage regulation loop involves subsystem (13). Moreover, based on the decoupling assumption, it is considered that the current tracking objective has been fulfilled after a relative short time, that is, \(\tilde{\varvec{i}}_{S,\alpha \beta }\rightarrow 0\). Otherwise, it is assumed that \(\varvec{e}_{\alpha \beta }\) is bounded. The latter turns out to be true if the terms at \(\varvec{e}_{\alpha \beta }\) as well as the adaptive estimations \(\hat{L}_S\) and \({\hat{R}}_S\) are bounded too. Therefore, subsystem (2) can be rewritten in terms of the increments of a new state \(z_2:=v_{C0}^2/2\) as follows,

where \(\tilde{z}_2:=(z_2-V_{ref}^2/2)\) and \(P^*\) is the control input. On the other hand, the voltage regulation control loop objective is established in terms of the average of the DC voltage, thus, it is equivalent to \(\langle z_2\rangle _0\rightarrow V_{ref}^2/2\). Therefore, the DC component of \(z_2\) is extracted of (23) which yields

where \(\tilde{z}_{20}\) represents the DC component of the state \(z_2\) and this can be obtained by the average of the state \(z_2\) in a definite time t by the following averaging operation

Hence, to assure \(\tilde{z}_{20}\rightarrow 0\) a controller is proposed as follows,

where the terms \(k_{pv}\), \(k_{iv}\) are positive gains that represent the proportional and integral gains of a PI controller; \(\tau\) is the time constant of a LPF. System (25)–(27) can be restructured in form of transfer function, that is,

where s represents the complex Laplace variable. It is important to note that, due to the rectification process an unavoidable second harmonic fluctuation appears in the current tracking loop. Hence, in the proposed control law, to guarantee the regulation of the DC component of \(z_2\) into its reference, a suitable filtering must be included to decrease the impact of such fluctuation. In order to establish a straightforward solution to solve these issues, a PI controller with a relatively low bandwidth is proposed (28). This controller ensures the DC voltage regulation of \(z_2\) unto its reference \(V_{ref}^2/2\), and reduces the impact of the harmonic fluctuation on the DC-link.

3.3 Overall proposed controller

By summarizing, the complete controller for the three-phase VSR consists of a current tracking loop formed by (29)–(31) and a voltage regulation loop shown in (32),

Observe that, the gain matrix \(\varvec{K}_i\) provides damping to the current tracking loop and the proportional terms associated with \(\hat{R}_S\) and \(\hat{L}_S\) compensate the parameter uncertainties of the input filter. Note that, the current reference \(\varvec{i}_{S,\alpha \beta }^*\) is constructed as follows,

where \(\Vert \varvec{v}_{\alpha \beta ,p}\Vert ^2\) is the square of the RMS value of \(\varvec{v}_{\alpha \beta ,p}\). In order to recuperate the control signal \(\varvec{u}_{\alpha \beta }\) from the control signal \(\varvec{e}_{\alpha \beta }\) the following expression is considered.

Remark 2:

The positive component estimation is obtained from (8), and it can be expressed in transfer function form as

where \(\varsigma\) represents a positive design gain that fixes the speed of response. The block diagram of the complete controller is shown in Fig. 2, which depicts the current tracking loop and the voltage regulation loop as described in the previous subsections.

3.4 Tuning guidelines

In this subsection the guidelines for tuning of the controller are presented in order to obtain a desired closed-loop performance. The development of these guidelines are based on the model of the system and the design of the controller.

3.4.1 Tuning guidelines: current tracking loop

As it has been established before, the tracking error \(\tilde{\varvec{i}}_{S,\alpha \beta }\) converges to zero as the control parameter \(\varvec{K}_{\varvec{i}}\) is positive definite. Nevertheless, more specific design rules for \(\varvec{K}_{\varvec{i}}\) are still necessary to achieve a desired dynamic performance. For this, recall that the current loop dynamics (18) is considered as the fastest dynamics for the overall system. This dynamics can be expressed as,

where \({\tilde{\varvec{\psi }}}_{\alpha \beta } :={\hat{\varvec{\psi }}}_{\alpha \beta } -\varvec{\psi }_{\alpha \beta }\), represents the disturbance rejection error. Notice that, the bandwidth of (34) is given by \(\omega _{BW\varvec{i}_{S,\alpha \beta }} =\varvec{K}_{\varvec{i}}/L_S\). Thus, it is proposed to tune \(\varvec{K}_{\varvec{i}}/L_S\) by fixing that each entry of \(\omega _{BW\varvec{i}_{S,\alpha \beta }}\) to be at most, 1/10 of the sampling frequency given by \(2\pi f_s\), that is, each entry of \(\omega _{BW\varvec{i}_{S,\alpha \beta }}\le \pi f_s/5\). Therefore, each entry of \(\varvec{K}_{\varvec{i}}\) must be less or equal than \(\pi f_sL_S/5\).

3.4.2 Tuning guidelines: voltage regulation loop

Guidelines for tuning controller parameters \(k_{iv}\) and \(k_{pv}\) in the voltage regulation loop can be obtained from the closed-loop subsystem (24)–(27), which can be rewritten as,

It is common in practice to select \(\tau \ll 1/(2\omega )\), where \(\omega\) is the fundamental frequency. Thus, the effect of the pole located at \(-1/\tau\) can be neglected as it is far enough with respect to the remaining dominant poles of the system (35)–(37). Therefore, the characteristic polynomial of the system can be reduced to,

and therefore, the natural oscillation frequency and the damping factor are shown next,

Now, if the damping factor is restricted to \(\chi \ge 1/\sqrt{2}\), the voltage dynamic must fulfill \(\omega _{BWV_C}\le \omega _{nv_{C0}}\). Moreover, to be consistent with the appealed time-scale separation, the bandwidth of \(\omega _{nv_{C0}}\) must be at most 1/10 the bandwidth of the current dynamics \(\omega _{BW\varvec{i}_{S,\alpha \beta }}\), i.e., \(\omega _{nv_{C0}}\le \omega _{BW\varvec{i}_{S,\alpha \beta }}\), which holds for \(\omega _{nv_{C0}}\le \omega _{BW\varvec{i}_{S,\alpha \beta }}/10\). Therefore, the parameters can be initially tuned as,

4 Experimental validation

The proposed controller in the last section has been experimentally validated in a 2 kW three-phase VSR PWM rectifier. The source voltage has been obtained from a Chroma 61705 programmable AC power supply that simulates a phase-to-ground fault to emulate an unbalanced operation in the grid voltage. Table 1 shows the vectors of the three-phase grid voltage in both balanced and unbalanced conditions. The experimental setup VSR rectifier is formed by three inductors \(L_S=3\) mH, three IGBT modules SKM100-GB124D, each module has a complete branch composed by two IGBTs in series connection, a capacitor \(C=1100 \ \mu\)F, and a DC-load which may change between R and RL. The resistance R has step changes from \(250\,\Omega\) to \(125\,\Omega\) and the inductor is fixed to \(L=3\)mH to RL DC-load. The DC-link voltage is fixed at \(V_{ref}=350\) V. The parameters of the overall system are shown in Table 2. The controller has been implemented in a dSPACE 1103 board with a sinusoidal modulation based on SPWM scheme has been used to generate the switching signal at a frequency of \(f_{sw}=12250\) Hz. The parameters used for the controller are shown in Table 3, which has been established following the guidelines presented in the previous section. In Fig. 3 the experimental setup of the VSR PWM rectifier is presented.

In this section experimental results are presented in order to validate the performance of the system under the proposed controller. The grid voltage is considered unbalanced with a voltage unbalance factor VUF between \(18.5\%\) and \(25\%\). A comparison of the proposed controller and a CMC controller that consists of a proportional term plus a bank of resonant filters as in [30], and that follows the ideas in [31], is also included in this section. The set of experimental results comprises the steady-state responses of the system and transient responses due to load step changes considering R and RL DC-loads after the bulky capacitor. A power quality analyzer was also used in order to present steady-state plots for voltage and current phasor representations, and THD and FFT experimental plots and values in order to show system response to poor power quality conditions at the grid voltage. Experimental results are performed under unbalanced and distorted grid voltages, unless otherwise specified.

Figure 4 shows the steady-state responses of [\(v_{1}, v_{2}, v_{3}\)] and the compensated lines currents [\(i_{S1}, i_{S2}, i_{S3}\)] under three different grid voltage conditions and with a resistive DC-load \(R=125\,\Omega\) from top to bottom. In Fig. 4b and c, a slight amount of grid voltage harmonic distortion can be noted which account for a THD\(_V\le 5\%\). As it can be observed in Fig. 4a, the grid voltage is balanced and free of harmonic distortion and the compensated line currents have sinusoidal waveforms and are in phase with the grid voltage. Therefore, the proposed control law is able to compensate the input currents under this grid voltage condition. Figure 4b and c show the steady-state responses under unbalanced and distorted grid voltage. It can be noted that the current mode controller also guarantees almost sinusoidal line currents and in phase with the positive sequence of the grid voltage despite of a VUF between \(18.5\%\) and \(25\%\) respectively. Notice that, in Fig. 4b and c, currents are in phase with \(v_{S1}\) which correspond to the positive sequence of the grid voltage. Figure 5a and b show (from top to bottom) the steady-state responses of [\(v_{1}, v_{2}, v_{3}\)] and the compensated lines currents [\(i_{S1}, i_{S2}, i_{S3}\)] under the same unbalanced grid voltage conditions however, the three-phase rectifier has an RL DC-load with \(R=125\,\Omega\) and \(L=3\) mH. It can be noted that, at both cases of grid voltage VUF \(=18.5\%\) and VUF \(=25\%\), the current mode controller is also able to assure sinusoidal currents and in phase with the positive sequence of grid voltages under this RL DC-load.

Figure 5c shows the performance of the grid currents of the PWM rectifier under the control law presented in [30] which consists of proportional term plus a bank of resonant filters. As it can be observed, if the grid voltage is unbalanced and distorted then the grid current is also unbalanced and distorted given that the control scheme does not consider a mechanism to deal with the grid voltage unbalanced. Notice also that, the proposed control law in this paper could be enhanced by using a similar strategy as in [30]. However, a bank of resonant filters in \(\alpha \beta\) coordinates must be added and tuned at odd harmonics of the fundamental frequency. Therefore, the control scheme would become highly bulky.

Figure 6 shows, from top to bottom, the time responses in steady-state of grid voltage [\(v_{1}, v_{2}, v_{3}\)] and the estimation of the positive-component of the grid voltages [\(\hat{v}_{1,p}, \hat{v}_{2,p}, \hat{v}_{3,p}\)] for the following conditions: \(\textcircled {1}\) balanced grid voltage and R DC-load; \(\textcircled {2}\) unbalanced grid voltage with a VUF \(=18.5\%\) and R DC-load; \(\textcircled {3}\) unbalanced grid voltage with a VUF \(=25\%\) and RL DC-load. The positive component of the grid voltage is used to construct the current reference for the inner control loop. Notice that the estimations of the positive component [\(\hat{v}_{1,p},\hat{v}_{2,p}, \hat{v}_{3,p}\)] are balanced sinusoidal signals under the three different conditions described above, however the amplitude changes when an unbalance condition appears in the grid voltage. As it was expected if the VUF increases then the amplitude of the positive components decreases.

Figure 7 shows, from top to bottom, the transient responses, during load step changes, of the capacitor voltage \(v_{C0}\) and the line currents [\(i_{S1}, i_{S2}, i_{S3}\)] when the resistance \(R\) is changed from \(R=250\, \Omega\) to \(R=125\, \Omega\) and back under different grid voltage conditions in the RL DC-load case. In Fig. 7a, the grid voltage is balanced and an R DC-load is considered. In Fig. 7b, the grid voltage is unbalanced with a VUF \(=18.5\%\) and DC-load is of R type. In Fig. 7c, the grid voltage is also unbalanced with a VUF \(=25\%\) and the DC-load consists of a resistance R in series with a fixed inductor \(L=3\) mH. As it can be observed, the proposed controller is capable of providing smooth transient responses, both in line currents and capacitor voltage and, reach the steady state in a relative short time. The controller is also able to regulate the capacitor voltage to a reference fixed at \(v_{C0}=350\,{\text{V}}\) maintaining a small DC voltage ripple \(\Delta v_{C0}\).

Figure 8 shows, from top to bottom, the transient responses of the power reference \(P^*\), the DC capacitor voltage \(v_{C0}\), the estimate of the filter inductance \(\hat{L}_S\) and the estimate of the series resistance \(\hat{R}_S\) under three different grid voltage conditions and DC-loads. In Fig. 8a, the input grid voltage is balanced and with R DC-load type. Figure 8b shows the transient responses under unbalanced grid voltage conditions with a VUF \(=18.5\%\) and a resistive DC-load R. Figure 8c shows performance for unbalance conditions with a VUF \(=25\%\) and an RL DC-load. Notice that, the estimation of the parameter \(\hat{L}_S\) and the parasitics resistance \(\hat{R}_S\) present small step changes during load changes, due to the increase of the rectifier power demand to the grid. Notice also that the output signal of the voltage control loop, \(P^*\), acts as a modulating signal which is used to calculate the current reference \(\varvec{i}_{S,\alpha \beta }^*\).

Figure 9 shows the voltage ripple at the DC output voltage (\(\Delta v_{C0}\)) under unbalanced grid voltage conditions with R and RL loads. It can be observed that the voltage ripple \(\Delta v_{C0}\) presents a fluctuation of 120 Hz, which is caused by the rectification process of the three-phase voltage PWM rectifier. Also notice that, under a \(\hbox {VUF}=25\%\) and RL DC-load the \(\Delta v_{C0}\) presents a small increment of amplitude therefore the maximum peak to peak amplitude is \(\Delta v_{C0}\le 5\) V. The DC-output capacitor filter has been designed follow the guidelines presented in [32].

Figure 10 shows the FFT analysis obtained with a FLUKE 435-II power quality analyzer (PQA) for the three current phases and their corresponding THD. Notice that, despite of the voltage unbalance factor, the harmonic distortion and the load connected to the rectifier, the proposed controller is able to maintain the total harmonic distortion less than \(5\%\). That means that the proposed controller is capable of guaranteeing a correct performance within the limits of harmonic distortion established by standards [3,4,5]. In Fig. 11, the three phase voltage and line currents vectors, under unbalanced conditions and with R and RL DC-loads, are shown. It can be observed that for a \(\hbox {VUF}=18.5\%\) the controller provides line currents in phase with the fundamental components of the three phase voltages. Meanwhile, if the \(\hbox {VUF}=25\%\), a small displacement of the current vectors with respect to the fundamental component of the voltage vectors is produced due to the high unbalance factor. Nevertheless, the controller is able to guarantee a three phase displacement power factor (\(\hbox {DPF}_{3\phi }\)) close to 1.00 and the three phase power factor (\(\hbox {PF}_{3\phi }\)) greater than or equal to 0.95 in all cases. Table 4 summarizes the \(\hbox {PF}_{3\phi }\), \(\hbox {DPF}_{3\phi }\) and the PF per phase (\(\phi _n\)) obtained by the PQA. It can be noted that the controller is able to keep a power factor \(\hbox {PF}_{3\phi }>0.95\) and the DPF close to 1.00 under different operation conditions.

5 Conclusion

This paper presented an adaptive current mode controller for a three-phase VSR. The main purpose of the proposed controller was to guarantee a proper line current tracking despite of the unbalanced and harmonic distortion in the grid voltage, by means of the use of the positive component of the grid voltage estimation. The controller also assures an adequate regulation of the capacitor voltage towards a desired reference. The controller was composed by two main loops, namely, current tracking loop and voltage regulation loop. The first one is formed by a proportional gain with a couple of estimators capable to deal with the uncertainties of the input filter. The last one consists in a PI controller which guarantees the delivery of a regulated voltage to the load. A relevant contribution in the controller was the introduction of three estimators. First the estimators of the series resistance and the inductance of the filter, allowed the system to be able to overcome the parametric uncertainties of the filter. Second the estimation of the positive component of the grid voltage, which allows to deliver sinusoidal line currents to the grid despite of the unbalanced and distortion conditions. Finally, experimental results were performed to validate the proposed controller in grid fault conditions.

References

Singh B, Singh BN, Chandra A et al (2003) A review of single-phase improved power quality AC–DC converters. IEEE Trans Ind Electron 50(5):962–981

Rodriguez JR, Dixon JW, Espinoza JR et al (2005) PWM regenerative rectifiers: state of the art. IEEE Trans Ind Electron 52(1):5–22

IEEE (1992) IEEE recommended practices and requirements for harmonics control in electric power systems. IEEE Std. 519

IEC (1995) Electromagnetic compatibility (EMC)-part 3: limits-Section 2: limits for harmonic current emissions. IEC1000-3-2

IEC (1990) Draft-revision of publication IEC 555-2: harmonics, equipment for connection to the public low voltage supply system. IEC SC 77A

Garcia O, Cobos JA, Prieto R et al (2003) Single phase power factor correction: a survey. IEEE Trans Power Electron 18(3):749–755

Maklakov AS, Radionov AA, Gasiyarov VR (2016) Power factor correction and minimization THD in industrial grid via reversible medium voltage AC drives based on 3L-NPC AFE rectifiers. In: Proceedings of IECON 42nd annual conference of the IEEE industrial electronics society, Florence, Italy, 23–26 October 2016, 6 pp

Martinez-Rodriguez PR, Escobar G, Valdez AA et al (2014) Direct power control of a three-phase rectifier based on positive sequence detection. IEEE Trans Ind Electron 61(8):4084–4092

Martinez PR, Escobar G, Sosa JM et al (2015) An improved current mode control of a three-phase rectifier based on positive-sequence detection. In: Proceedings of IECON 41st annual conference of the IEEE industrial electronics society, Yokohama, Japan, 9–12 November 2015, 6 pp

Ge J, Zhao Z, Yuan L et al (2015) Direct power control based on natural switching surface for three-phase PWM rectifiers. IEEE Trans Power Electron 30(6):2918–2922

Zhang Y, Qu C (2015) Model predictive direct power control of PWM rectifiers under unbalanced network conditions. IEEE Trans Ind Electron 62(7):4011–4022

Zhang Y, Peng Y, Qu C (2016) Model predictive control and direct power control for PWM rectifiers with active power ripple minimization. IEEE Trans Ind Appl 52(6):4909–4918

Cho Y, Lee KB (2016) Virtual-flux-based predictive direct power control of three-phase PWM rectifiers with fast dynamic response. IEEE Trans Power Electron 31(4):3348–3359

Trinh QN, Wang P, Choo FH (2017) An improved control strategy of three-phase PWM rectifiers under input voltage distortions and DC offset measurement errors. IEEE J Emerg Sel Top Power Electron 5(3):1164–1176

Si G, Zhao W, Guo Z et al (2014) A novel double closed loops control strategy of three-phase voltage source PWM rectifier with disturbances. In: Proceedings of 33rd Chinese control conference, Nanjing, China, 28–30 July 2014, 5 pp

Mohamed A, Salehi V, Mohammed O (2012) Reactive power compensation in hybrid AC/DC networks for smart grid applications. In: Proceedings of 3rd IEEE PES innovative smart grid technologies Europe (ISGT Europe), Berlin, Germany, 14–17 October 2012, 6 pp

Maklakov AS, Radionov AA (2014) Integration prospects of electric drives based on back to back converters in industrial smart grid. In: Proceedings of 12th international conference on actual problems of electronics instrument engineering (APEIE), Novosibirsk, Russia, 2–4 October 2014, 5 pp

Xu G, Yu W, Griffith D et al (2017) Towards integrating distributed energy resources and storage devices in smart grid. IEEE Internet Things J 4(1):192–204

Bollen MHJ, Das R, Djokic S et al (2017) Power quality concerns in implementing smart distribution-grid applications. IEEE Trans Smart Grid 8(1):391–399

Hadjikypris M, Marjanovic O, Terzija V (2016) Damping of inter-area power oscillations in hybrid AC–DC power systems based on supervisory control scheme utilizing FACTS and HVDC. In: Proceedings of power systems computation conference (PSCC), Genoa, Italy, 20–24 June 2016, 7 pp

Kini PG, Bansal RC, Aithal RS (2007) A novel approach toward interpretation and application of voltage unbalance factor. IEEE Trans Ind Electron 54(4):2315–2322

Anwari M, Hiendro A (2010) New unbalance factor for estimating performance of a three-phase induction motor with under- and overvoltage unbalance. IEEE Trans Energy Convers 25(3):619–625

Fang ZJ, Cai T, Duan SX et al (2015) Performance analysis and capacitor design of three-phase uncontrolled rectifier in slightly unbalanced grid. IET Power Electron 8(8):1429–1439

Zhang Y, Qu C, Gao J (2017) Performance improvement of direct power control of PWM rectifier under unbalanced network. IEEE Trans Power Electron 32(3):2319–2328

Zhang Y, Gao J, Qu C (2017) Relationship between two direct power control methods for PWM rectifiers under unbalanced network. IEEE Trans Power Electron 32(5):4084–4094

Luo A, Jin G, Xiao H et al (2014) Simple control method for three-phase pulse-width modulation rectifier of switching power supply under unbalanced and distorted supply voltages. IET Power Electron 7(10):2572–2581

Lee K, Jahns TM, Lipo TA et al (2009) Observer-based control methods for combined source-voltage harmonics and unbalance disturbances in PWM voltage–source converters. IEEE Trans Ind Appl 45(6):2010–2021

Escobar G, Martinez-Montejano MF, Valdez AA et al (2011) Fixed reference frame phase-locked loop (FRF-PLL) for grid synchronization under unbalanced operation. IEEE Trans Ind Electron 58(5):1943–1951

Escobar G, Martinez-Montejano MF, Olguin RET et al (2008) An adaptive direct power control for three-phase PWM rectifier in the unbalanced case. In: Proceedings of 39th IEEE power electronics specialists conference, Rhodes, Greece, 15–19 June 2008, 6 pp

Tang H, Zhao R, Tang S et al (2012) Control of three-phase PWM boost rectifiers in stationary frame using proportional-resonant controller. In: Proceedings of IEEE international symposium on industrial electronics, Hangzhou, China, 28–31 May 2012, 5 pp

Teodorescu R, Blaabjerg F, Liserre M et al (2006) Proportional-resonant controllers and filters for grid-connected voltage–source converters. IEEE Proc Electr Power Appl 153(5):750–762

Moran L, Ziogas PD, Joos G (1992) Design aspects of synchronous PWM rectifier-inverter systems under unbalanced input voltage conditions. IEEE Trans Ind Appl 28(6):1286–1293

Author information

Authors and Affiliations

Corresponding author

Additional information

CrossCheck date: 27 December 2017

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

MARTÍNEZ-RODRIGEZ, P.R., SOSA, J.M., ITURRIAGA-MEDINA, S. et al. Model based current mode control design and experimental validation for a \(3\phi\) rectifier under unbalanced grid voltage conditions. J. Mod. Power Syst. Clean Energy 6, 777–790 (2018). https://doi.org/10.1007/s40565-018-0400-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40565-018-0400-x