Abstract

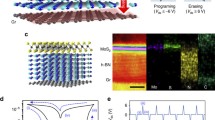

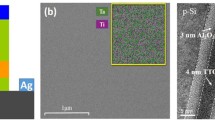

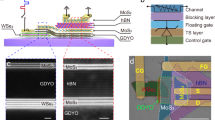

Atomically thin two-dimensional (2D) materials have emerged as promising candidates for flexible and transparent electronic applications. Here, we introduce non-volatile charge trapping memory devices, based on the 2D heterostructure field-effect transistor consisting of a few-layer MoS2 channel and CrPS4 charge-trapping gate stack. Clockwise hysteresis behaviors in transfer curves measured at room temperature show strong dependence on the thickness of CrPS4, which are attributed to charge trapping at trap sites in the CrPS4 layers. Our heterostructure memory device with 75 nm-thick CrPS4 layer exhibits both large memory windows up to 100 V and a high on/off current ratio (3 \(\times\) 105) with good endurance during 625 cycles because of excellent trapping ability of trap sites in the CrPS4. Especially, the memory window size can be effectively tuned from 7.6 to 100 V by changing the sweep range of gate voltage. Such high performances of the charge-trapping memory device with a simple heterostructure provide a promising route towards next-generation memory devices utilizing 2D materials.

Similar content being viewed by others

References

S. Manzeli et al., Nat. Rev. Mater. 2, 17033 (2017)

J. Shim et al., Adv. Electron. Mater. 3, 1600364 (2017)

Z. Zhang et al., InfoMat. 2, 261–290 (2020)

F. Liao et al., ACS Appl. Electron. Mater. 2, 111–119 (2020)

B.W.H. Baugher et al., Nano Lett. 13, 4212–4216 (2013)

J. Late et al., ACS Nano 6, 5635–5641 (2012)

Y. Guo et al., Appl. Phys. Lett. 106, 103109 (2015)

N. Kaushik et al., npj 2D Mater. Appl. 1, 34 (2017)

A. Di Bartolomeo et al. 2D Materials 5, 1 (2018)

K.L. Ganapathi et al., Semicond. Sci. Technol. 34, 055016 (2019)

F.S. Yang et al., Nat. Commun. 11, 2972 (2020)

K. Yang et al., Nanomaterials 10, 1471 (2020)

E. Zhang et al., ACS Nano 9, 612–619 (2015)

C. Lee et al., Nanotechnology 29, 335202 (2018)

S.P. Wang et al., Adv. Electron. Mater. 5, 1800726 (2019)

G.-H. Lee et al., APL Mater. 2, 092511 (2014)

J. Lee et al., ACS Nano 11, 10935–10944 (2017)

S. Ding et al., J. Phys. Condens. Matter 32, 405804 (2020)

M. Shin et al., J. Korean Phys. Soc. 76, 8 (2020)

R. Frisenda et al., Chem. Soc. Rev. 47, 53–68 (2018)

Q. Feng et al., Nanoscale 8, 2686–2692 (2016)

M. Chen et al., ACS Nano 8, 4023–4032 (2014)

H.J. Kim et al., Nanoscale 10, 17557–17566 (2018)

M. Zhang et al., Nanophotonics 9, 2475–2486 (2020)

S. Bertolazzi et al., ACS Nano 7, 3246–3252 (2013)

C.C. Lu et al., ACS Nano 6, 4469–4474 (2012)

P. Xia et al., Sci. Rep. 7, 40669 (2017)

M.J. Lee et al., NPG Asia Mater. 12, 82 (2020)

Acknowledgements

This work was supported by National Research Foundation of Korea (NRF) grants funded by the Korea government (MSIP) (No. 2013R1A3A2042120) and the Nano Material Technology Development Program through the NRF funded by the MSIP (No. 2016M3A7B4909668). The work at CQM and SNU was supported by the Leading Researcher Program of NRF (No. 2020R1A3B2079375). This paper was supported by Konkuk University Researcher Fund in 2019.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations

Rights and permissions

About this article

Cite this article

Shin, M., Lee, M.J., Yoon, C. et al. Charge-trapping memory device based on a heterostructure of MoS2 and CrPS4. J. Korean Phys. Soc. 78, 816–821 (2021). https://doi.org/10.1007/s40042-021-00154-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40042-021-00154-7