Abstract

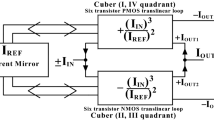

A new current-mode fractional-power CMOS circuit such as cube-root and squared-cube-root configurations that give output signal in four quadrants has been presented for the first time. MOSFETs utilized in the design exploit translinear principle in weak-inversion region. The second-order effects on the circuit proposition have been analysed. The implementation justification has been validated by post-layout simulation on Virtuoso-SPECTRE tool with 180 nm GPDK CMOS process parameters. It has been found that using ± 0.5 V supply voltage, the realized cube-root and squared-cube-root circuits work for an input range of ± 30 µA while consuming few hundred nano-watts of static power and exhibit a maximum of ± 1 dB error over a wide input range of ± 1.5 µA to ± 30 µA in all four quadrants. Utility of the proposed circuits, as companding and gamma corrector, has also been elaborated.

Similar content being viewed by others

References

Ruggiero, J.F.: Analog Mathematical Root Extractor. United States Patent 1975, Patent No. 3916180

Abuelmatti, M.T.: Universal CMOS current-mode analog function synthesizer. IEEE Trans. Circuits Syst. Fund Theory Appl. 49(10), 1468–1474 (2002)

Dutta, D.; Ujjwal, R.; Banerjee, S.; Serdijn, W.A.: Design of static and dynamic translinear circuits based on CMOS CCII translinear loops. In: IEEE Conference. https://doi.org/10.1109/ICECS.2005.4633466 (2006)

Menekay, S.; Tarcan, R.C.; Kuntman, H.: Novel high-precision current-mode circuits based on the MOS-translinear principle. Int. J. Electron. Commun. (AEÜ) 63(11), 992–997 (2009)

Lin, K.J.; Cheng, C.J.; Su, H.C.; Yu, B.: Design of CMOS current-controlled-gamma corrector. IJEC (AEU) 65, 997–1005 (2011)

Sleczak, J.; Petrzela, J.: Evolutionary synthesis of cube root computational circuit using graph hybrid estimation of distribution algorithm. Radio Eng. 23(1), 549–558 (2014)

Woo, S.H.; Hwang, S.H.; Lee, K.; Koo, H.S.; Cho, G.H.: Wideband wide-tunable current mode gamma corrector for HDTV applications. Electron. Lett. 35(23), 1988–1989 (1999)

Lin, K.J.; Cheng, C.J.; Chiu, S.F.; Su, H.C.: CMOS current-mode selectable S-shape correction circuit. In: Proceedings of 9th WSEAS International Conference on Instrumentation, Measurement, Circuits and Systems, pp. 70–75 (2010)

Lin, K.J.; Cheng, C.J.; Chen, J.E.; CMOS current-mode companding multiplier/divider and its Nth-root. In: Proceedings of the 9th WSEAS International Conference on Instrumentation, Measurement, Circuits and Systems (2010)

Putra, R.V.W.; Adiono, T.: Optimized hardware algorithm for integer cube root calculation and its efficient architecture. In: International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), pp. 263–267 (2015)

Hamiane, M.: Modeling and simulation of a CMOS-based analog function generator. IJECE 4(4), 532–538 (2014)

Datta, D.; Ray, B.; Banerjee, A.: Synthesis of linear and non-linear analog circuits. In: 2019 32nd IEEE International System-on-Chip Conference (2020)

Bhanja, M.; Ray, B.N.: Synthesis procedure of configurable building block based linear and nonlinear analog circuits. IEEE Trans. Comput. Aided Des. Circuits Syst. 36(12), 1940–1953 (2017)

Lin, K.J.; Cheng, C.J.; Chiu, S.F.; Su, H.C.: CMOS current-mode implementation of fractional-power functions. CSSP 31, 61–75 (2012)

Mishra, S.K.; Gupta, M.; Upadhyay, D.K.: Fractional derivative of logarithmic function and its applications as multipurpose ASP circuit. AICSP 100, 377–387 (2019)

Arai, M.; Sano, Y.: Exponentiation conversion circuit capable of changing the power exponent to any value. AICSP (2021). https://doi.org/10.1007/s10470-021-01873-4

Naderi, A.; Khoei, A.; Hadidi, K.: Circuit implementation of high-resolution rational powered membership functions in standard CMOS technology. Analog Integr. Circuits Signal Process. 65(2), 217–223 (2010)

Popa, C.R.: Synthesis of Computational Structures for Analog Signal Processing. Springer (2011) https://doi.org/10.1007/978-1-4614-0403-3

Tsirimokou, G.; Psychalinos, C.; Elwakil, A.: Design of CMOS Analog Integrated Fractional-Order Circuits, 1st edn. Springer (2017)

Allen, P.E.; Holberg, D.R.: CMOS Analog Circuit Design, 3rd edn. Oxford University Press (2011)

Shaterian, M.; Twigg, C.M.; Azhari, J.: An MTL-based configurable block for current-mode nonlinear analog computation. IEEE Trans. Circuits Syst. Express Briefs 60(9), 587–591 (2013)

Moshfe, S.; Hoseini, P.; Khoei, A.; Hadidi, K.: A fully programmable analog CMOS rational-powered membership function generator with continuously adjustable high precision parameters. Circuits Syst. Signal Process. 33(5), 1337–1352 (2014)

Varshney, G.; Pandey, N.; Pandey, G.: Electronically tunable multifunction transadmittance-mode fractional-order filter. Arab. J. Sci. Eng. 46, 1067–1078 (2020)

D’Angelo, R.J.; Sonkusale, S.R.: A time-mode translinear principle for nonlinear analog computation. IEEE Trans. Circuits Syst. I Regul. Pap. 62(9), 2187–2195 (2015)

Guardia, C.M.; Boemo, E.: FPGA implementation of a binary32 floating point cube root. In: Proceedings of Southern Conference on Programmable Logic, pp. 1–6 (2014)

Sapargaliyev, A.; Kalganova, T.G.: Open-ended evolution to discover analogue circuits for beyond conventional applications. Genet. Program Evol. Mach. 13, 411–443 (2012)

Pyle, S.D.; Thangavel, V.; Williams, S.V.; DeMara, R.F: Self-scaling evolution of analog computation circuits with digital accuracy refinement. In: NASA/ESA Conference on Adaptive Hardware and Systems (2015)

Wang, Y.; Wang, P.; Huang, C.; Sun, J.: Five-input cube-root logical operation based on DNA strand displacement. J. Nanoelectron. Optoelectron. 13(6), 831–838 (2018)

Zhou, C.; Geng, H.; Wang, P.; Guo, C.: Ten-input cube root logic computation with rational designed DNA nanoswitches coupled with DNA strand displacement process. ACS Appl. Mater. Interfaces 12(2), 2601–2606 (2020)

Srivastava, P.; Sharma, R.K.: A novel exponential approximation with ± 0.21 dB error for realizing an improved CMOS exponential function generator. CSSP 36(7), 2941–2957 (2017)

Srivastava, P.; Sharma, R.K.; Ranjan, R.K.: On the realisation of current-mode four-quadrant CMOS cuber. Analog Integr. Circuits Signal Process. 99(1), 47–61 (2018)

Srivastava, P.; Sharma, R.K.: A novel pseudo-Taylor-exponential approximation technique for input-output range extension with reduced linearity error and its current-mode CMOS implementation. Arab. J. Sci. Eng. (2021). https://doi.org/10.1007/s13369-021-05495-w

Elwakil, A.; Maundy, B.; Elamien, M.B.; Belostotski, L.: A four-quadrant current multiplier/divider cell with four transistors. Analog Integr. Circ. Sig. Process. 95, 173–179 (2018)

Schlottmann, C.R.; Abramson, D.; Hasler, P.E.: A MITE-based translinear FPAA. IEEE Trans. VLSI Syst. 20(1), 1–9 (2012)

Marticorena-Arraiza, M.; De La Cruz Blas, C.A.; Algueta-Miguel, J.M.; Lopez-Martin, A.: A 1.2-V current-mode RMS-to-DC converter based on a novel two-quadrant electronically simulated MOS translinear loop. IEEE Trans. Circuits Syst. Express Briefs 67(3), 420–424 (2020)

Maryan, M.M.; Azhari, S.J.; Ghanaatian, A.: An up-down topology based-current mode adjustable-gain square-rooting/geometric-mean circuit. Analog Integr. Circuits Signal Process. 102, 283–291 (2020)

Srivastava, P.; Sharma, R.K.: On V-V/V-I type double balanced CMOS multiplier utilizing triode-region translinear principle. Analog Integr. Circuits Signal Process. 104, 229–241 (2019)

Maryan, M.M.; Azhari, S.J.: CMOS design of computational current-mode static and dynamic functions based on analog translinear cell. Comput. Electric. Eng. 68, 629–645 (2018)

Maryan, M.M.; Ghanaatian, A.; Azhari, S.J.; Abrishamifar, A.: Low-power high-speed analog multiplier/divider based on a new current squarer circuit. Arab. J. Sci. Eng. 43, 2909–2918 (2018)

Al-Absi, M.A.: A new highly accurate CMOS current-mode four-quadrant multiplier. Arab. J. Sci. Eng. 40(51), 551–558 (2014)

Bansal, U.; Masiwal, P.; Yadav, M.; Raj, N.: Four-quadrant CMOS analog current multiplier using frequency compensation and 1.5 V supply. Arab. J. Sci. Eng. (2021). https://doi.org/10.1007/s13369-021-05563-1

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Srivastava, P., Sharma, R.K. & Ranjan, R.K. On the Realization of Current-Mode Four-Quadrant CMOS Fractional Power and Cube-Root Converter. Arab J Sci Eng 47, 13837–13855 (2022). https://doi.org/10.1007/s13369-021-06488-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-021-06488-5