Abstract

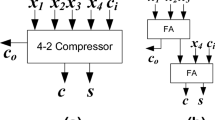

This paper proposes a novel full adder based on the linear threshold gate (LTG) which belongs to the single-electron-device (SED) family. The advantage of an LTG-based circuit is that it has a satisfactory fan-out as opposed to other SED-based circuits; hence, it can be utilized in any complex circuit network. The proposed full adder is utilized as an application in a 4-2 compressor architecture. Compressors are elementary building blocks which are widely used in arithmetic structures such as multipliers. The proposed 4-2 compressor can operate reliably in any tree structured parallel multiplier due to its high performance full adders. The SIMON simulator demonstrates the correct operation of the proposed full adder design, along with the presented 4-2 compressor. The performance of proposed full adder and the 4-2 compressor, in terms of delay and power consumption, are calculated in complete detail. The comparisons indicate that the proposed full adder has the highest speed in comparison with the previous high speed designs.

Similar content being viewed by others

References

Hutchby J.A., Bourianoff G.I., Zhirnov V.V., Brewer J.E.: Extending the road beyond CMOS. IEEE Circuits Devices Mag. 18, 28–41 (2002)

Likharev K.K.: Single-electron devices and their applications. IEEE Proc. 87(4), 606–632 (1999)

Korotkov A.: Single-electron logic and memory devices. Int. J. Electron. 86(5), 511–547 (1999)

Lageweg, C.; Cotofana, S.; Vassiliadis, S.: A linear threshold gate implementation in single-electron technology. IEEE Computer Society Workshop on VLSI, pp. 93–98 (2001)

Chen, C.; Mao, Y.: A statistical reliability model for single-electron threshold logic. IEEE Trans. Electron Devices 55(5), 1547–1553 (2008)

Booth A.D.: A signed binary multiplication technique. Quart. J. Mech. Appl. Math. 4, 236–240 (1951)

Wallace, C.S.: A suggestion for a fast multiplier. IEEE Trans. Electron. Comput. EC-13, 14–17 (1964)

Nazarov, Y.N.; Vyshenskii, S.V.: SET circuits for digital applications. In: Koch, H.; Lubbig, H. (eds.) Single-Electron Tunneling and Mesoscopic Devices, vol. 31. Ser. Electron. Photon., pp. 61–66. Springer, Berlin (1992)

Lageweg C., Cotofana S., Vassiliadis S.: Single-electron encoded latches and flip-flops. IEEE Trans. Nanotechnol 3, 237–248 (2004)

Tucker J.R.: Complementary digital logic based on the Coulomb blockade. J. Appl. Phys. 72, 4399–4413 (1992)

Sharifi, M.J.: A theoretical study of the performance of a single-electron transistor buffer. IEICE Trans. Electron. E94-C, 1105–1111 (2011)

Cotofana, S.; Lageweg, C.; Vassiliadis, S.: On effective computation with nanodevices: a single-electron tunnelling technology case study. In: Proceedings of the International Conference Semiconductor 4-6 October 2004

Bahrepour, D.; Sharifi, M.J.: A new single-electron tunneling cell based on linear threshold gate. Int. Conf. on Enabling Science and Nanotechnol. (ESciNano), 1–2 December 2010

Lageweg, C.; Cotofana, S.; Vassiliadis, S.: Binary multiplication based on single-electron tunneling. In: Proceedings of the 15th IEEE International Conference on Application-Specific Systems, Architectures and Processors, pp. 152–166 (2004)

Rehan, S.E.: A novel half-adder using single-electron tunneling technology. In: 2nd IEEE International Conference on Nano/Micro Engineered and Molecular Systems, pp. 245–249 (2007)

Zardalidis G.T., Karafyllidis I.: A single-electron half-adder. Microelectron. J. 33, 265–269 (2002)

Wasshuber C., Kosina H., Selberherr S.: SIMON—a simulator for single-electron tunnel devices and circuits. IEEE Trans. Computer Aided Design. 16, 937–944 (1997)

Gooraji, F.A.; Sharifi, M.J.; Bahrepour, D.: A time-dependent spice model for single-electron box and its application to logic gates at low and high temperatures. In: International Conference on Enabling Science and Nanotechnol (ESciNano), 1–2 December 2010

Sharifi M.J.: Transient response of single-electron devices and their time constants. J. Korean Phys. Soc. 58(1), 138–149 (2011)

Sulieman, M.H.; Beiu, V.: On single-electron technology full adders. IEEE Trans. Nanotechnol. 4(5), 669– 680 (2005)

Lee J., Lee J.H., Chung I.-Y, Kim C.-J., Park B.-G., Kim D.M., Kim D.H.: Comparative study on energy-efficiencies of single-electron transistor-based binary full adders including non-ideal effects. IEEE Trans. Nanotechnol. 10, 1180–1190 (2011)

Iwamura, H.; Akazawa, M.; Amemiya, Y.: Single-electron majority logic circuits. IEICE Trans. Electron. E81-C, 42–48 (1998)

Ono Y., Inokawa H., Takahashi Y.: Binary adders of multi-gate single-electron transistor: specific design using pass-transistor logic. IEEE Trans. Nanotechnol. 1, 93–99 (2002)

Lageweg C., Cotofana S., Vassiliadis S.: A full adder implementation using set based linear threshold gates. 9th Int. Conf. Electron. Circuits Syst. 2, 665–668 (2002)

Oya T., Asai T., Fukui T., Amemiya Y.: A majority logic device using an irreversible single-electron box. IEEE Trans. Nanotechnol. 2, 15–22 (2003)

Lageweg, C.R.; Cotofana, S.D.; Vassiliadis, S.: 7/3 and 7/2 Counters implemented in single-electron technology. Proc. ProRISC 2002, pp. 344–350 (2002)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bahrepour, D., Sharifi, M.J. A Novel High Speed Full Adder Based on Linear Threshold Gate and its Application to a 4-2 Compressor. Arab J Sci Eng 38, 3041–3050 (2013). https://doi.org/10.1007/s13369-013-0615-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-013-0615-0