Abstract

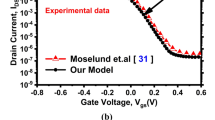

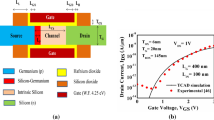

The noise behavior of a proposed Ge-source counter-doped pocket-based double-gate tunnel FET (GS-PNPN-TFET) in the presence and absence of interfacial trap charge conditions is presented. The noise behavior was studied in terms of drain current noise power spectral density (Sid, unit A2/Hz) and gate voltage electron noise power spectral density (Svgee, unit V2/Hz) against variation of various device parameters, viz., body thickness (Tsi), pocket length (Lp), gate-oxide thickness (Tox), gate-oxide material, mole fraction, and doping density using Sentaurus TCAD software. Oxide–semiconductor interfacial trap charge of Gaussian distribution was used at two frequencies − 1 MHz and 10 GHz. Our analysis also includes the impact of temperature variation on noise. As per our findings, the noise spectrums are comparable for the presence and absence of interfacial trap charges in the proposed TFET. This is because the noise spectrum depends on on-current (ION) and the ION is negligibly influenced by the interfacial trap charges in the proposed TFET. However, off-current (IOFF) degrades when trap charges are present at the interface. In comparison with other FET devices, the proposed device offers improved Sid and Svgee values of roughly 1.82 × 10–29 A2/Hz and 5.5 × 10–20 V2/Hz, respectively, at 10 GHz frequency. Furthermore, the diffusion noise predominates at higher frequencies, while the generation–recombination noise is found to be dominant at low frequencies, as expected. Flicker noise is most noticeable at low and medium frequencies but fades away at higher frequencies.

Similar content being viewed by others

References

Q Zhang, W Zhao and A Seabaugh IEEE Electron Dev. Lett. 27 297 (2006).

A M Ionescu and H Riel Nature 479 329 (2011).

K Boucart and A M Ionescu IEEE trans. on electron dev. 54 1725 (2007).

A Chauhan, G Saini and K Yerur Superlattices microstruct. 124 79 (2018).

S B Rahi, P Asthana and S Gupta Journal of Comp. Elect. 16 30 (2017).

L K Vandamme, X Li and D Rigaud IEEE Trans. on Electron Dev. 41 1936 (1994).

R Pandey, B Rajamohanan, H Liu, V Narayanan and S Datta IEEE Trans. on Electron Dev. 61 552 (2013).

F S Neves, P G Agopian, J A Martino, B Cretu, R Rooyackers, A Vandooren, E Simoen, A V Y Thean and C Claeys IEEE Trans. on Electron Dev. 63 1658 (2016).

R Goswami and B Bhowmick Baishya Superlattices Microstruct. 86 342 (2015).

M Haartman and M Östling (Springer Science & Business Media) (2007)

F N Hooge IEEE Trans. on electron dev. 41 1926 (1994).

J Xu and M J Deen Electronics Letters 38 429 (2002).

P Ghosh and B Bhowmick Applied Phys. A 124 1 (2018).

J Talukdar, G Rawat, K Singh and K Mummaneni Silicon 13 3971 (2021).

K Baruah, R Das and S Baishya Applied Phys. A 126 1 (2020).

S Chander, S K Sinha and R Chaudhary Superlattices Microstruct. 161 107101 (2022).

K Baruah R G Debnath and S Baishya (Micro and Nanoelectronics Dev., Circuits and Systems (MNDCS)) (Singapore: Springer) (2022)

S Bhattacherjee, S Roy, G Chakroborty and U Ray Journal of Physics Conf. Series 1797 1 (2021).

H J Shin et al Japanese Journal of Applied Phys. 59 10 100903 (2020).

A Goel, S Rewari, S Verma and S Gupta Journal of Elect. Materials 50 108 (2021).

N Damrongplasit, C Shin, S H Kim, R A Vega and T J K Liu IEEE trans. on electron dev. 58 3541 (2011).

V Nagavarapu, R Jhaveri and J C Woo IEEE Trans. on Electron Dev. 55 1013 (2008).

W Li and J C Woo IEEE Trans on Electron Dev. 67 1480 (2020).

M Liu, M Cai, B Yu and Y Taur IEEE trans. on electron dev. 53 3146 (2006).

R Goswami and B Bhowmick Procedia Computer Sci. 93 125 (2016).

G Lee, J S Jang and W Y Choi Semiconductor sci and tech. 28 052001 (2013).

H G Virani, R B R Adari and A Kottantharayil IEEE trans. on electron dev. 57 2410 (2010).

Sentaurus Device User Guide, Version K-2015.06, (2015)

S Datta, H Liu and V Narayanan Microelectronics Reliab. 54 861 (2014).

J P Nougier IEEE Trans on Electron Dev. 41 2034 (1994).

R Bijesh, D K Mohata, H Liu and S. Datta 70th Device Research Conf. IEEE, p 203 (2012)

S H Kim, H Kam, C Hu and T J K Liu 2009 Symposium on VLSI Tech. IEEE p 178 (2009)

J Wan, C Le Royer, A Zaslavsky and S Cristoloveanu Applied Phys. Letters 97 243503 (2010).

M Hellenbrand, E Memišević, M Berg, O P Kilpi, J Svensson and L E Wernersson IEEE Electron Dev. Lett. 38 1520 (2017).

K Roy Barman and S Baishya Applied Phys. A 125 401 (2019).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Baruah, K., Baishya, S. Electrical noise in Ge-source double-gate PNPN tunnel field effect transistor. Indian J Phys 97, 1473–1485 (2023). https://doi.org/10.1007/s12648-022-02508-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12648-022-02508-8