Abstract

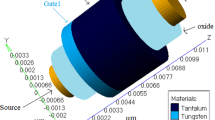

This paper presents the design and analysis of a vertical dopingless double gate junctionless field-effect transistor (VDL-DG-JLFET) on a silicon-on-insulator (SOI) substrate, utilizing the charge plasma concept. 2D TCAD numerical simulations have been carried out to evaluate and compare switching and analog/ RF performance parameters with a vertical double gate junctionless accumulation field-effect transistor (VDG-JAMFET). The results demonstrate that the VDL-DG-JLFET exhibits superior gate control and delivers substantial enhancements in critical parameters such as drive current (ID), reduction of drain-induced barriers (DIBL), subthreshold swing (SS), and the on-current to off-current ratio (ION/IOFF) when juxtaposed with the VDG-JAMFET. Additionally, the VDL-DG-JLFET demonstrates improved transconductance (gm), cut-off frequency (fT), and maximum oscillation frequency (fmax) compared to the VDG-JAMFET. These findings collectively highlight the superior attributes of the VDL-DG-JLFET in comparison to the VDG-JAMFET, reinforcing its potential for advanced electronic applications.

Similar content being viewed by others

References

Lee C, Afzalian A, Akhavan ND et al (2009) Junctionless multigate field-effect transistor Junctionless multigate field-effect transistor. Appl Phys Lett 94:053511. https://doi.org/10.1063/1.3079411

Colinge J-P, Lee C-W, Afzalian A et al (2010) Nanowire transistors without junctions. Nat Nanotechnol 5:225–229. https://doi.org/10.1038/nnano.2010.15

Colinge JP, Kranti A, Yan R et al (2011) Junctionless Nanowire Transistor (JNT): properties and design guidelines. Solid State Electron 65–66:33–37. https://doi.org/10.1016/j.sse.2011.06.004

Jin X, Liu X, Wu M et al (2013) A unified analytical continuous current modelapplicable to accumulation mode (junctionless) and inversion mode MOSFETs withsymmetric and asymmetric double-gate structures. Solid-State Electron 79:206–209. https://doi.org/10.1016/j.sse.2012.08.003

Holtij T, GraefM HFM et al (2014) Compact model for short-channel junctionlessaccumulation mode double gate mosfets. IEEE Trans Electron Devices 61(2):288–299. https://doi.org/10.1109/TED.2013.2281615

Bavir M, Abbasi A, Orouji AA (2019) A simulation study of junctionless double-gate metal-oxide-semiconductor field-effect transistor with symmetrical side gates. SILICON. https://doi.org/10.1007/s12633-019-00258-7

Sahu C, Singh J (2014) Charge-plasma based process variation immune junctionlesstransistor. IEEE Electron Device Lett 35(3):411–413. https://doi.org/10.1109/LED.2013.2297451

Sahu C, Singh J (2015) Potential benefits and sensitivity analysis of dopinglesstransistor for low power applications. IEEE Trans Electron Devices 62(3):729–735. https://doi.org/10.1109/TED.2015.2389900

Hueting RJE, Rajasekharan B, Salm C et al (2008) The charge plasma P-N diode. IEEE Electron Device Lett 29(12):1367–1369. https://doi.org/10.1109/LED.2008.2006864

Rajasekharan B, Hueting RJE, Salm C et al (2010) Fabrication and characterizationof the charge-plasma diode. IEEE Electron Device Lett 31(6):528–530. https://doi.org/10.1109/LED.2010.2045731

Singh S, Raman A (2018) Gate-all-around charge plasma-based dual material gate-stack nanowire fet for enhanced analog performance. IEEE Trans Electron Devices 65(7):3026–3032. https://doi.org/10.1109/TED.2018.2816898

Wadhwa G, Raj B (2018) Parametric variation analysis of symmetric double gatecharge plasma jltfet for biosensor application. IEEE Sens J 18(15):6070–6077. https://doi.org/10.1109/JSEN.2018.2846409

Amin I, Sarin R (2016) Enhanced analog performance of doping-less dual materialand gate stacked architecture of junctionless transistor with high-k spacer. Appl Phys A 122. https://doi.org/10.1007/s00339-016-9904-2

Panchore M, Singh J, Mohanty SP (2016) Impact of channel hot carrier effectin junction-and doping-free devices and circuits. IEEE Trans Electron Devices 63(12):5068–5071. https://doi.org/10.1109/TED.2016.2619621

Ramaswamy S, Kumar MJ (2016) Raised source/drain dopingless junctionless accu-mulation mode FET: Design and analysis. IEEE Trans Electron Devices 63(11):4185–4190. https://doi.org/10.1109/TED.2016.2612263

Sirohi A, Sahu C, Singh J (2019) Analog/RF performance investigation of dopinglessFET for ultra-low power applications. IEEE Access 7:141810–141816. https://doi.org/10.1109/ACCESS.2019.2937444

Verma PK, Verma YK, Mishra V, Gupta SK (2020) A charge-plasma-based dual-metal-gate recessed-source/drain dopingless junctionless transistor with enhanced analog and RF performance. J Comput Electron 19:1085–1099. https://doi.org/10.1007/s10825-020-01528-z

Verma P, Gupta S (2021) An improved analog/RF and linearity performances withsmall-signal parameter extraction of virtually doped recessed source/drain dopin-gless junctionless transistor for radio-frequency applications. Silicon 13:1519–1539. https://doi.org/10.1007/s12633-020-00518-x

Raushan M, Bashir MY, Alam N et al (2022) Performance improvement of dopinglesstransistor for low power applications. SILICON 14:12. https://doi.org/10.1007/s12633-021-01556-9

Kumar R, Panchore M (2022) Impact of back gate bias on analog performance of dop-ingless transistor. Trans Electr Electron Mater 24. https://doi.org/10.1007/s42341-022-00426-4

Garg A, Singh Y, Singh B (2020) Dual-channel junctionless FETs for improved analog/RF performance. Silicon. https://doi.org/10.1007/s12633-020-00545-8

(2016)Atlas : A 2-D Device Simulator. Silvaco international, Santa Clara

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

All authors participated in shaping and conceptualizing the study. Aanchal Garg conducted material preparation, TCAD simulation, and analysis. Balraj Singh and Yashvir Singh were responsible for the formal analysis and investigation of the simulated results. Aanchal Garg initially drafted the manuscript, which was then revised and edited by Balraj Singh and Yashvir Singh.

Corresponding author

Ethics declarations

Ethics Approval

The information within this manuscript is entirely original and has not been previously published or copyrighted. Furthermore, the content presented in this document is not currently being reviewed for publication in any other source.

Consent to Participate

Authors agree.

Consent of Publications

Upon submission of the manuscript, the authors agree not to withdraw the manuscript at any stage before a final decision from the Editor of SILICON.

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Garg, A., Singh, B. & Singh, Y. Vertical Dopingless Dual-Gate Junctionless FET for Digital and RF Analog Applications. Silicon 16, 2719–2728 (2024). https://doi.org/10.1007/s12633-024-02873-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-024-02873-5