Abstract

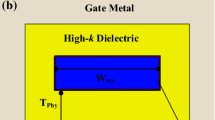

Vertical Nanosheet Transistors serves as a potential substitute for the Nanowire and FinFET architecture at advanced technology nodes on account of higher drive current and superior control of short channel effects. In this article, a novel analysis of various stacked high-K dielectrics in n-type Vertical C-shaped Silicon Channel Nanosheet Field Effect Transistor (nVCNFET) is implemented. In-depth analysis is done on the effects of stacked high-K dielectrics on nVCNFET device performance and short channel effects. The nVCNFET with optimized gate oxide stack of Al2O3-TiO2 exhibits a remarkable current ratio of 3.2 × 1016, which is 107 times efficient over the reported Vertical Nanosheet FETs (NSFET) up to date. The Device performance and scaling compatibility of nVCNFET for sub-10 nm and 5 nm technology nodes are demonstrated to certify the device’s reliability. On the contrary, the proposed nVCNFET maintains ideal Subthreshold Swing (< 60 mV/decade) and yields 60% lesser DIBL value (8 mV/V) over the other Silicon-NSFETs. This concludes nVCNFET, a befitting candidate for low power and Dynamic Random Access Memory (DRAM) applications.

Similar content being viewed by others

Data Availability

Not applicable.

References

Liu H, Neal AT, Ye PD (2012) Channel length scaling of MoS 2 MOSFETs. ACS Nano 6:8563–8569. https://doi.org/10.1021/nn303513c

Kim S, Lee K, Kim S, Kim M, Lee JH, Kim S, Park BG (2022) Investigation of device performance for fin angle optimization in FinFET and gate-all-around FETs for 3 nm-node and beyond. IEEE Trans Electron Dev 69:2088–2093. https://doi.org/10.1109/TED.2022.3154683

Sachid AB, Chen MC, Hu C (2017) Bulk FinFET with low-κ spacers for continued scaling. IEEE Trans Electron Dev 64:1861–1864. https://doi.org/10.1109/TED.2017.2664798

Yu E, Heo K, Cho S (2018) Characterization and optimization of inverted-T FinFET under nanoscale dimensions. IEEE Trans Electron Dev 65:3521–3527. https://doi.org/10.1109/TED.2018.2846478

Niimi H, Liu Z, Gluschenkov O, Mochizuki S, Fronheiser J, Li J, Demarest J, Zhang C, Liu B, Yang J, Raymond M, Haran B, Bu H, Yamashita T (2016) Sub-10-9 Ω-cm2 n-type contact resistivity for FinFET technology. IEEE Electron Device Lett 37:1371–1374. https://doi.org/10.1109/LED.2016.2610480

Thomas S (2018) Nanosheet FETs at 3 nm. Nat Electron 1:613. https://doi.org/10.1038/s41928-018-0179-9

Hur J, Lee BH, Kang MH, Ahn DC, Bang T, Jeon SB, Choi YK (2016) Comprehensive analysis of gate-induced drain leakage in vertically stacked nanowire FETs: inversion-mode versus junctionless mode. IEEE Electron Device Lett 37:541–544. https://doi.org/10.1109/LED.2016.2540645

Capogreco E, Witters L, Arimura H, Sebaai F, Porret C, Hikavyy A, Loo R, Milenin AP, Eneman G, Favia P, Bender H, Wostyn K, Dentoni EL, Schulze A, Vrancken OA, Mitard J, Langer R, Holsteyns F, Waldron N, Barla K, Heyn VD, Mocuta D, Collaert N (2018) First demonstration of vertically stacked gate-all-around highly strained germanium nanowire pFETs. IEEE Trans Electron Dev 65:5145–5150. https://doi.org/10.1109/TED.2018.2871595

Chung CCC, Shen CH, Lin JY, Chin CC, Chao TS (2018) Vertically stacked cantilever n-type poly-Si junctionless nanowire transistor and its series resistance limit. IEEE Trans Electron Dev 65:756–762. https://doi.org/10.1109/TED.2017.2780851

Georgiou T, Jalil R, Belle BD, Britnell L, Gorbachev RV, Morozov SV, Kim YJ, Gholinia A, Haigh SJ, Makarovsky O, Eaves L, Ponomarenko LA, Geim AK, Novoselov KS, Mishchenko A (2013) Vertical field-effect transistor based on graphene-WS 2 heterostructures for flexible and transparent electronics. Nat Nanotechnol 8:100–103. https://doi.org/10.1038/nnano.2012.224

Tan C, Yu M, Tang J, Gao X, Yin Y, Zhang Y, Wang J, Gao X, Zhang C, Zhou X, Zheng L, Liu H, Jiang K, Ding F, Peng H (2023) 2D fin field-effect transistors integrated with epitaxial high-k gate oxide. Nature 616:66–72. https://doi.org/10.1038/s41586-023-05797-z

Jagannathan H, Anderson B, Sohn CW, Tsutsui G, Strane J, Xie R, Fan S, Kim KI, Song S, Sieg S, Seshadri I, Mochizuki S, Wang J, Rahman A, Cheon KY, Hwang I, Demarest J, Do J, Fullam J, Jo G, Hong B, Jung Y, Kim M, Kim S, Lallement R, Levin T, Li J, Miller E, Montanini P, Pujari R, Osborn C, Sankarapandian M, Son GH, Waskiewicz C, Wu H, Yim J, Young A, Zhang C, Varghese A, Robison R, Burns S, Zhao K, Yamashita T, Dechene D, Guo D, Divakaruni R, Wu T, Seo KI, Bu H (2021) Vertical-transport nanosheet technology for CMOS scaling beyond lateral-transport devices. Tech Dig Int Electron Devices Meet (IEDM). 26.1.1–26.1.4. https://doi.org/10.1109/IEDM19574.2021.9720561

Yakimets D, Eneman G, Schuddinck P, Bao TH, Bardon MG, Raghavan P, Veloso A, Collaert N, Mercha A, Verkest D, Thean AVY, Meyer KD (2015) Vertical GAAFETs for the ultimate CMOS scaling. IEEE Trans Electron Dev 62:1433–1439. https://doi.org/10.1109/TED.2015.2414924

Sung PJ, Chang CY, Chen LY, Kao KH, Su CJ, Liao TH, Fang CC, Wang CJ, Hong TC, Jao CY, Hsu HS, Luo SX, Wang YS, Huang HF, Li JH, Huang YC, Hsueh FK, Wu CT, Huang YM, Hou FJ, Luo GL, Huang YC, Shen YL, Ma WCY, Huang KP, Lin KL, Samukawa S, Li Y, Huang GW, Lee YJ, Li JY, Wu WF, Shieh JM, Chao TS, Yeh WK, Wang YH (2018) Voltage transfer characteristic matching by different nanosheet layer numbers of vertically stacked junctionless CMOS inverter for SoP/3D-ICs applications. Tech Dig Int Electron Devices Meet IEDM 21.4.1–21.4.4. https://doi.org/10.1109/IEDM.2018.8614553

Gundu AK, Kursun V (2023) 5-nm gate-all-around transistor technology with 3-D stacked nanosheets. IEEE Trans Electron Dev 69:922–929. https://doi.org/10.1109/TED.2022.3143774

Valasa S, Tayal S, Thoutam LR (2023) Performance analysis of metal gate engineered junctionless nanosheet fet with a ft/fmax of 224/342ghz for beyond 5g (b5g) applications. Micro Nanostruct 179. https://doi.org/10.1016/j.micrna.2023.207582

Yadav N, Jadav S, Saini G (2023) Impact of gate length and doping variation on the DC and analog/RF performance of sub - 3nm stacked si gate-all-around nanosheet FET. SILICON 15:217–228. https://doi.org/10.1007/s12633-022-01989-w

Yadav N, Jadav S, Saini G (2022) Geometrical variability impact on the performance of sub - 3 nm gate-all-around stacked nanosheet FET. SILICON 14:10681–10693. https://doi.org/10.1007/s12633-022-01770-z

Li OW, Wang YQ, Cheng SL, You HL (2023) Impact of process variability in vertically stacked junctionless nanosheet FET. SILICON 15:2765–2780. https://doi.org/10.1007/s12633-022-02203-7

Sreenivasulu VB, Narendar V (2022) Design and temperature assessment of junctionless nanosheet FET for nanoscale applications. SILICON 14:3823–3834. https://doi.org/10.1007/s12633-021-01145-w

Srivastava S, Shashidhara M, Acharya A (2022) Investigation of self-heating effect in tree-FETs by interbridging stacked nanosheets: a reliability perspective. IEEE Trans Device Mater Reliab 23:58–63. https://doi.org/10.1109/TDMR.2022.3227942

Sun Y, Li X, Liu Z, Liu Y, Li X, Shi Y (2021) Vertically stacked nanosheets tree-type reconfigurable transistor with improved ON-current. IEEE Trans Electron Dev 69:370–374. https://doi.org/10.1109/TED.2021.3126266

Rathore S, Jaisawal RK, Kondekar PN, Bagga N (2022) Design optimization of three-stacked nanosheet FET from self-heating effects perspective. IEEE Trans Device Mater Reliab 22:396–402. https://doi.org/10.1109/TDMR.2022.3181672

Huang BW, Tsai CE, Liu YC, Tu CT, Hsieh WH, Jan SR, Chen YR, Chueh SJ, Cheng CY, Liu CW (2022) Highly stacked GeSn nanosheets by CVD epitaxy and highly selective isotropic dry etching. IEEE Trans Electron Dev 69:2130–2136. https://doi.org/10.1109/TED.2022.3144105

Ansari MHR, Li H, El-Atab N (2023) Vertically stacked nanosheet FET: charge- trapping memory and synapse with linear weight adjustability for neuromorphic computing applications. IEEE Trans Electron Dev 70:1344–1350. https://doi.org/10.1109/TED.2023.3234018

Tsai MJ, Peng KH, Sun CJ, Yan SC, Hsu CC, Lin YR, Lin YH, Wu YC (2019) Fabrication and characterization of stacked poly-si nanosheet with gate-all-around and multi-gate junctionless field effect transistors. IEEE J Electron Devices Soc 7:1133–1139. https://doi.org/10.1109/JEDS.2019.2952150

Xiao ZR, Zhu HL, Wang Q, Chen Z, Liu ZY, Zhang YK, Yan ZJ, Shi YF, Zhou N, Li JJ, Gao JF, Ai XZ, Lu SS, Huang WX, Xiong WJ, Kong ZZ, Xiang JJ, Zhang Y, Zhao J, Liu JB, Lu YH, Bai GB, He XB, Du AY, Yang H, Yang T, Wu ZH, Li JF, Luo J, Wang WW, Ye TC (2023) Vertical N-type and P-type nanosheet FETs with C-shaped channel. IEEE Trans Electron Dev 70:1380–1385. https://doi.org/10.1109/TED.2023.3239048

Belkhiria M, Echouchene F, Jaba N, Bajahzar A, Belmabrouk H (2020) Impact of high-k gate dielectric on self-heating effects in PiFETs structure. IEEE Trans Electron Dev 67:3522–3529. https://doi.org/10.1109/TED.2020.3012418

Xiao ZR, Wang Q, Zhu HL, Chen Z, Zhang YK, Li JJ, Zhou N, Gao JF, Ai XZ, Lu SS, Huang WX, Xiong WJ, Kong ZZ, Xiang JJ, Zhang Y, Zhao J, Liu JB, Lu YH, Bai GB, He XB, Du AY, Wu ZH, Yang T, Li JF, Luo J, Wang WW, Ye TC (2022) Vertical C-shaped-channel nanosheet FETs featured with precise control of both channel-thickness and gate-length. IEEE Electron Device Lett 43:1183–1186. https://doi.org/10.1109/LED.2022.3187006

Atlas device simulation User’s Manual (2015) Silvaco Int., Santa Clara

Ancona MG, Yu Z, Dutton RW, Vande Voorde PJ, Cao M, Vook D (2000) Density-gradient analysis of MOS tunneling. IEEE Trans Electron Dev 47:2310–2319. https://doi.org/10.1109/16.887013

Jain G, Sawhney RS, Kumar R, Saini A (2023) Design and comparative analysis of heterogeneous gate dielectric nanosheet TFET with temperature variance. SILICON 15:187–196. https://doi.org/10.1007/s12633-022-02013-x

Zhang Y, Ai X, Yin X, Zhu H, Yang H, Wang GL, Li JJ, Du AY, Li C, Huang WX, Xie L, Li YY, Liu YB, Zhang YB, Jia KP, Wu ZH, Ma XL, Zhang QZ, Mao SJ, Xu GB, Xiang JJ, Gao JF, He XB, Lu YH, Bai GB, Zhao J, Li YL, Yang T, Li JF, Yin HX, Radamson H, Luo J, Zhao C, Wang WW, Ye TC (2021) Vertical sandwich GAA FETs with self-aligned high-k metal gate made by quasi atomic layer etching process. IEEE Trans Electron Dev 68:2604–2610. https://doi.org/10.1109/TED.2021.3072879

Ramesh S, Ivanov T, Putcha V, Alian A, Hernandez AS, Rooyackers R, Camerotto E, Milenin A, Pinna N, Kazzi SE, Veloso A, Lin D, Lagrain P, Favia P, Collaert N, Meye KD (2017) Record performance top-down in 0 . 53 Ga 0 . 47 as vertical nanowire FETs and vertical nanosheets. Tech Dig Int Electron Devices Meet (IEDM). 409–412. https://doi.org/10.1109/IEDM.2017.8268406

Veloso A, Eneman G, Bao TH, Chasin A, Simoen E, Vecchio E, Devriendt K, Brus S, Rosseel E, Hikavyy A, Loo R, Paraschiv V, Chan BT, Radisic D, Li W, Versluijs JJ, Teugels L, Sebaai F, Favia P, Bender H, Vancoille E, Scheerder JE, Fleischmann C, Horiguchi N, Matagne P (2019) Vertical nanowire and nanosheet FETs: device features, novel schemes for improved process control and enhanced mobility, potential for faster & more energy efficient circuits. Tech Dig Int Electron Devices Meet (IEDM). 11.1.1–11.1.4. https://doi.org/10.1109/IEDM19573.2019.8993602

Yin X, Zhang Y, Zhu H, Wang GL, Li JJ, Du AY, Li C, Zhao LH, Huang WX, Yang H, Xie L, Ai XZ, Zhang YB, Jia KP, Wu ZH, Ma XL, Zhang QZ, Mao SJ, Xiang JJ, Gao JF, He XB, Bai GB, Lu YH, Zhou N, Kong ZZ, Zhang Y, Zhao J, Ma SS, Xuan ZH, Li YY, Li L, Zhang QH, Han JH, Chen RL, Qu Y, Yang T, Luo J, Li JF, Yin HX, Radamson H, Zhao C, Wang WW, Ye TC (2020) Vertical sandwich gate-all-around field-effect transistors with self-aligned high-k metal gates and small effective-gate-length variation. IEEE Electron Device Lett 41:8–11. https://doi.org/10.1109/LED.2019.2954537

Li C, Zhu H, Zhang Y, Wang Q, Yin X, Li J, Wang G, Kong Z, Ai X, Xie L, Liu Y, Li Y, Huang W, Yan Z, Xiao Z, Radamson HH, Li J, Wang W (2021) First demonstration of novel vertical gate-all-around field-effect- transistors featured by self-aligned and replaced high - κ metal gates. Nano Lett 21:4730–4737. https://doi.org/10.1021/acs.nanolett.1c01033

International Roadmap for Device and Systems (IRDS) (2023) https://irds.ieee.org/editions/2023. Accessed Oct 2023

Acknowledgements

The authors acknowledge Karunya Institute of Technology and Sciences, Coimbatore, India for providing the support and facility to carry out this research work.

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

Miss. Angelin Delighta A and Dr. D. Nirmal have role in Conceptualization, Methodology, Writing Original Draft, Validation and Investigation. Dr. Binola K Jebalin. I.V, Mr. S. Angen Franklin and Dr. J. Ajayan have the credits to Software, Formal analysis, Resources, Data Curation, Writing Review and Editing.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

All procedures performed in studies were in accordance with the ethical standards of the institutional and/or national research committee and with the comparable ethical standards.

For this type of study formal consent is not required.

Consent for Publication

Authors give consent for the publication of the Submitted Research article in Silicon.

Research involving Human Participants and/or Animals

Not applicable.

Informed Consent

Not applicable.

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

A, A.D., I.V, B.K.J., Ajayan, J. et al. A new Vertical C-shaped Silicon Channel Nanosheet FET with Stacked High-K Dielectrics for Low Power Applications. Silicon 16, 2659–2670 (2024). https://doi.org/10.1007/s12633-024-02871-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-024-02871-7