Abstract

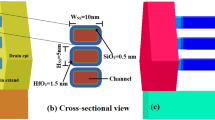

Vertically Stacked Nanosheet TFET (VNS-TFET) can break the subthreshold swing limit of MOSFETs and achieve higher layout efficiency. Due to the scaled-down device size, VNS-TEFT becomes vulnerable to process variability during fabrication. In this paper, the statistical impedance field method (sIFM) is used to investigate the effects of process variability, such as random doping fluctuations (RDF), work function variation (WFV), and oxide thickness variation (OTV), on VNS-TEFT. The standard deviation of the threshold voltage (σV th) is used to measure the effects of doping concentration, gate metal grain-related parameters and device parameters on the device process variability. The TCAD simulation results show that choosing an appropriate doping concentration for the source region can effectively reduce the effects of RDF. As the average grain size increases, the effect on WFV and OTV increases, but RDF has no effect. In addition, using a physical gate oxide with higher-κ in the VNS-TFET can effectively suppress WFV. Finally, it can be seen that the RDF is most sensitive to the size variation of the VNS-TFET.

Similar content being viewed by others

Data Availability

Data available on request from the authors.

Code Availability

The referred papers will be available on request.

References

Singh P, Samajdar DP, Yadav DS (2021) A low power single gate l-shaped tfet for high frequency application. In: 2021 6Th international conference for convergence in technology (i2CT)

Goswami B, Sengupta SJ, Reja W, Das P, Sarkar SK (2021) Validation of input/output characteristics of symmetrical double source tfet device. In: 2021 Devices for integrated circuit (devIC)

Mustakim N, Hussain S, Saha JK (2020) Characterization of charge plasma-based junctionless tunneling field effect transistor (jl-tfet). In: 2020 IEEE International symposium on smart electronic systems (iSES) (formerly inis)

Kim JH, Kim S, Park BG (2019) Double-gate tfet with vertical channel sandwiched by lightly doped si. IEEE Trans Electron Devices 66(4):1656–1661

Sahu SA, Mohapatra SK, Goswami R (2018) Comparative analysis of double gate tfet and hetero dielectric double gate tfet. In: 2018 International conference on applied electromagnetics, signal processing and communication (AESPC), vol 1, pp 1–4, DOI https://doi.org/10.1109/AESPC44649.2018.9033293

Kang MJ, Myeong I, Fobelets K (2020) Geometrical influence on self heating in nanowire and nanosheet fets using tcad simulations. In: 2020 4Th IEEE electron devices technology manufacturing conference (EDTM), pp 1–4. https://doi.org/10.1109/EDTM47692.2020.9117971

Dash TP, Dey S, Mohapatra E, Das S, Jena J, Maiti CK (2019) Vertically-stacked silicon nanosheet field effect transistors at 3nm technology nodes. In: 2019 Devices for integrated circuit (devIC), pp 99–103. https://doi.org/10.1109/DEVIC.2019.8783300

Yoon J-S, Jeong J, Lee S, Baek R-H (2018) Multi-strategies of 7-nm node nanosheet fets with limited nanosheet spacing. IEEE Journal of the Electron Devices Society 6:861–865. https://doi.org/10.1109/JEDS.2018.2859799

Loubet N, Hook T, Montanini P, Yeung CW, Khare M (2017) Stacked nanosheet gate-all-around transistor to enable scaling beyond finfet. In: 2017 Symposium on VLSI technology

Barraud S, Lapras V, Previtali B, Samson MP, Lacord J, Martinie S, Jaud M-A, Athanasiou S, Triozon F, Rozeau O, Hartmann JM, Vizioz C, Comboroure C, Andrieu F, Barbé JC, Vinet M, Ernst T (2017) Performance and design considerations for gate-all-around stacked-nanowires fets. In: 2017 IEEE International electron devices meeting (IEDM), pp 29–212924. https://doi.org/10.1109/IEDM.2017.8268473

Jegadheesan V, Sivasankaran K, Konar A (2019) Impact of geometrical parameters and substrate on analog/rf performance of stacked nanosheet field effect transistor. Mater Sci Semicond Process 93:188–195

Yoon JS, Baek RH (2020) A novel sub-5-nm node dual-workfunction folded cascode nanosheet fets for low power mobile applications. IEEE Access 8

Thoti N, Li Y, Sung W-L (2021) Significance of work function fluctuations in sige/si hetero-nanosheet tunnel-fet at sub-3 nm nodes. IEEE Transactions on Electron Devices 1–5. https://doi.org/10.1109/TED.2021.3130497

Lee R, Lee J, Lee K, Kim S, Ahn H, Kim S, Kim H-M, Kim C, Lee J-H, Kim S, Park B-G (2021) Vertically-stacked si0.2ge0.8 nanosheet tunnel fet with 70 mv/dec average subthreshold swing. IEEE Electron Device Lett 42(7):962–965. https://doi.org/10.1109/LED.2021.3079246

Thoti N, Li Y, Reddy KS, Samukawa S (2020) High-performance metal-ferroeletric- semiconductor nanosheet line tunneling field effect transistors with strained sige. In: International conference on simulation of semiconductor processes and devices (SISPAD)

Damrongplasit N, Kim SH, Liu T (2013) Study of random dopant fluctuation induced variability in the raised-ge-source tfet. Electron Device Letters, IEEE

Huang WT, Li Y (2014) The impact of fin/sidewall/gate line edge roughness on trapezoidal bulk finfet devices. In: International conference on simulation of semiconductor processes & devices

Gu L, Liang R, Xu J, Ren TL, Wang J (2018) Study of work-function variation effects in multigate tunneling field effect transistors. In: IEEE International conference on electron devices and solid state circuits

Lee H, Park JD, Shin C (2016) Study of random variation in germanium-source vertical tunnel fet. IEEE Trans Electron Devices 63(5):1827–1834

Park J, Lee H, Oh S, Shin C (2016) Design for variation-immunity in sub-10-nm stacked-nanowire fets to suppress ler-induced random variations. IEEE Trans Electron Devices 63(12):5048–5054

Trojman L (2016) Study of mobility for hfo2 dielectric fdsoi-uttb pmos under substrate biases. IEEE Lat Am Trans 14(10):4235–4240. https://doi.org/10.1109/TLA.2016.7786299

Vimala P, Ss S, Krishna LL, Bassapuri M, Manikanta T (2020) Characteristic analysis of silicon nanowire tunnel field effect transistor (nw-tfet). In: 2020 IEEE International conference on electronics, computing and communication technologies (CONECCT), pp 1–4. https://doi.org/10.1109/CONECCT50063.2020.9198578

Reid D, Millar C, Roy S, Asenov A (2011) Statistical enhancement of the evaluation of combined rdd- and ler-induced vT variability: Lessons from 105 sample simulations. IEEE Trans Electron Devices 58(8):2257–2265. https://doi.org/10.1109/TED.2011.2147317

El Sayed K, Lyumkis E, Wettstein A (2012) Modeling statistical variability with the impedance field method. In: Proc. Int. Conf. Simulation semiconductor process. Devices (SISPAD), pp 205–208

2018 sentaurus device user guide version k-2018.06

Wettstein A, Sayed KE, Lyumkis E (2012) Modeling statistical variability with the impedance field method

Bae MS, Yun I (2020) Impact of process variability in junctionless finfets due to random dopant fluctuation, gate work function variation, and oxide thickness variation. Semiconductor science and technology 35 (3):035015–10350158

Tsai M-J, Peng K-H, Sun C-J, Yan S-C, Hsu C-C, Lin Y-R, Lin Y-H, Wu Y-C (2019) Fabrication and characterization of stacked poly-si nanosheet with gate-all-around and multi-gate junctionless field effect transistors. IEEE Journal of the Electron Devices Society 7:1133–1139. https://doi.org/10.1109/JEDS.2019.2952150

Damrongplasit N, Shin C, Kim SH, Vega RA, King Liu TJ (2011) Study of random dopant fluctuation effects in germanium-source tunnel fets. IEEE Trans Electron Devices 58(10):3541–3548

Acknowledgements

The authors would like to thank the ERCESI group at the School of Computer Science, Northwestern Polytechnical University for their guidance in writing and revising the paper.

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

Yuehui Han designed and performed the experiments, analyzed the results, prepared the figures, and wrote the manuscript.

Ru Han supervised the entire research, coordinated with author and analyzed the results.

Yuefeng Gu analyzed the results.

Liangyou Feng prepared the figure.

Corresponding author

Ethics declarations

Ethics approval

The authors declare that they have no known competing financial interest or personal relationships that could have appeared to influence the work reported in this paper.

Conflict of Interests

Authors declare no conflict of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Gu Yuefeng and Feng Liangyou are contributed equally to this work.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Yuehui, H., Ru, H., Yuefeng, G. et al. Impact of Process Variability on Threshold Voltage in Vertically-Stacked Nanosheet TFET. Silicon 15, 4529–4537 (2023). https://doi.org/10.1007/s12633-022-02256-8

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-02256-8