Abstract

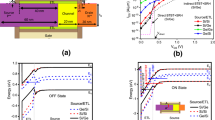

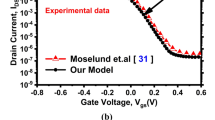

Tunnel field-effect transistors have demonstrated a predominant performance in the field of semiconductors. However, low drive current and ambipolarity are major challenges for TFETs. To overcome these challenges, a Partially Extended Germaniumn source DG-TFET (PEGeDG-TFET) is proposed. This PEGeDG-TFET structure has a partially extended Ge source under the gate below the Si-epitaxial layer to improve vertical tunneling, using the overlap area concept and pocket layer to enhance lateral tunneling along with suppressed Short-Channel effect. After scaling the transistor dimension up to 40%, the proposed device performance is not only retained but greatly improved by device engineering techniques. Further, a complete metal gate contact is deployed over the Si-epi layer length and overlapping the source metal-contact over oxide width touching Si-epi layer width. The proposed device study reveals the impact of source length, dielectric material, and oxide thickness variation. It also comprehends the impact of Ge molar fraction on transfer characteristics, transconductance, RF parameters (ft,GBP, etc). Further, the Linearity analysis in Si1−xGex source in PEDG-TFET with x varying from 0 to 1.The proposed device claims ION to be 3.2 mA/um, IOFF = 3.21 × 10− 17 A/um with an ION / IOFF ratio of 9.6 × 1013 along with enhanced transconductance, cut-off frequency, and gain-bandwidth product. The potential of the proposed device for digital logic applications are examined for the worst case (equal source and drain doping), and it is demonstrated in this work along with Analog/RF applications.

Similar content being viewed by others

Data Availability

All the data taken from another resource has been given the corresponding reference. The data, for which reference is not provided, is the original data.

References

Ratnesh RK, Goel A, Kaushik G, Garg H, Singh CM, Prasad B (2021) . Mater Sci Semicond Process 134:106002. https://doi.org/10.1016/j.mssp.2021.106002

Roy K, Mukhopadhyay S, Mahmoodi-Meimand H (2003) . Proc IEEE 91(2):305. https://doi.org/10.1109/JPROC.2002.808156

Taur Y, Buchanan D, Chen W, Frank D, Ismail K, Lo SH, Sai-Halasz G, Viswanathan R, Wann HJ, Wind S, Wong HS (1997) . Proc IEEE 85(4):486. https://doi.org/10.1109/5.573737

Raj B, Saxena A, Dasgupta S (2011) . IEEE Circ Syst Mag 11 (3):38. https://doi.org/10.1109/MCAS.2011.942068

Bala S, Khosla M (2018) . Superlattices Microstruct 124:160. https://doi.org/10.1016/j.spmi.2018.10.007

Thoti N, Lakshmi B (2017) . Mater Sci Semicond Process 71:304. https://doi.org/10.1016/j.mssp.2017.08.014

Kao KH, Verhulst AS, Vandenberghe WG, Soree B, Groeseneken G, De Meyer K (2012) . IEEE Trans Electron Devices 59(2):292. https://doi.org/10.1109/TED.2011.2175228

Bhuwalka KK, Schulze J, Eisele I (2005) IEEE Trans Electron Devices 52(5):909. https://doi.org/10.1109/TED.2005.846318

Raad BR, Nigam K, Sharma D, Kondekar PN (2016) . Superlattices Microstruct 94:138. https://doi.org/10.1016/j.spmi.2016.04.016

Acharya A, Solanki AB, Glass S, Zhao QT, Anand B (2019) . IEEE Trans Electron Devices 66(9):4081. https://doi.org/10.1109/TED.2019.2927001

Paras N, Chauhan SS (2019) . Microelectron Eng 216:111043. https://doi.org/10.1016/j.mee.2019.111043

Paras N, Chauhan SS (2019) Microelectron Eng 217. https://doi.org/10.1016/j.mee.2019.111103

Kr Singh O, Kaur B (2021) .. In: 2021 IEEE international conference on technology, research, and innovation for betterment of society (TRIBES). https://doi.org/10.1109/TRIBES52498.2021.9751635, pp 1–6

Jhaveri R, Nagavarapu V, Woo JCS (2011) . IEEE Trans Electron Devices 58(1):80. https://doi.org/10.1109/TED.2010.2089525

Kim JH, Kim S, Park BG (2019) . IEEE Trans Electron Devices 66(4):1656. https://doi.org/10.1109/TED.2019.2899206

Kujur Kanak SS (2022) Rasheed Gadarapulla, Silicon. https://doi.org/10.1007/s12633-022-01737-0

Alassery Fawaz SS, Asif Irshad K (2022) Silicon. https://doi.org/10.1007/s12633-021-01647-7

Loan ASA, Rafat M (2018) . IEEE Trans Electron Devices 65(2):763. https://doi.org/10.1109/TED.2017.2783764

Kim SW, Kim JH, Member S, Liu T.j.K., Choi WY, Park B.g., An A (2016) L.s. Fet 63(4):1774

Chen S, Wang S, Liu H, Li W, Wang Q, Wang X (2017) . IEEE Trans Electron Devices 64(3):1343. https://doi.org/10.1109/TED.2017.2647809

Chen S, Liu H, Wang S, Li W, Wang X, Zhao L (2018) Analog / RF performance of T-shape gate dual-source tunnel field-effect transistor. Nanoscale Res Lett 13:321. https://doi.org/10.1186/s11671-018-2723-y

Sharma S, Basu R, Kaur B (2022) . IEEE Trans Electron Devices 69(5):2692. https://doi.org/10.1109/TED.2022.3156895

Vadizadeh M (2021) . IEEE Trans Electron Devices 68(4):1986. https://doi.org/10.1109/TED.2021.3056632

Wadhwa G, Raj B (2018) . IEEE Sensors J 18(15):6070. https://doi.org/10.1109/JSEN.2018.2846409

Joshi T, Singh Y, Singh B (2020) . IEEE Trans Electron Devices 67(4):1873. https://doi.org/10.1109/TED.2020.2973353

Sandeep Kumar BS, Singh Y (2021) . Silicon 6(13):1805. https://doi.org/10.1007/S12633-020-00565-4

Chawla T, Khosla M, Raj B (2022) . Mater Sci Semicond Process 145:106643. https://doi.org/10.1016/j.mssp.2022.106643

Pasupathy GLR, Manivannan S (2021) . Silicon 14:1887. https://doi.org/10.1007/s12633-021-01018-2

Venkatesh M, Priya GL, Balamurugan NB (2021) . Silicon 13(3):911. https://doi.org/10.1007/s12633-020-00856-w

Banerjee S, Garg S, Saurabh S (2018) . IEEE Electron Device Lett 39(5):773. https://doi.org/10.1109/LED.2018.2819205

Garg S, Saurabh S (2020) . IEEE J Exploratory Solid-State Computat Devices Circ 6(2):146. https://doi.org/10.1109/JXCDC.2020.3038073

Pillarisetty R, Kung B, Corcoran S, Dewey G, Kavalieros J, Kennel H, Kotlyar R, Le V, Lionberger D, Metz M, Mukherjee N, Nah J (2010) Technical Digest - International Electron Devices Meeting IEDM. https://doi.org/10.1109/IEDM.2010.5703312

Tezuka T, haru Sugiyama N, Takagi S (2001) . Appl Phys Lett 79:1798

Liow TY, Tan KM, Yeo YC, Agarwal A, Du A, Tung CH, Balasubramanian N (2005) . Appl Phys Lett 87:262104

Kao KH, Verhulst AS, Vandenberghe WG, De Meyer K (2013) . IEEE Trans Electron Devices 60(1):6. https://doi.org/10.1109/TED.2012.2227115

Kao KH, Verhulst AS, Vandenberghe WG, Soree B, Magnus W, Leonelli D, Groeseneken G, De Meyer K (2012) . IEEE Trans Electron Devices 59(8):2070. https://doi.org/10.1109/TED.2012.2200489

Chang HY, Adams B, Chien PY, Li J, Woo JCS (2013) . IEEE Trans Electron Devices 60(1):92. https://doi.org/10.1109/TED.2012.2228006

Zhang Y (2016) U.S Patent 9252250 B2

Ye H, Yu J (2014) . Sci Technol Adv Mater 15(2):024601. https://doi.org/10.1088/1468-6996/15/2/024601

Wang PY, Tsui BY (2015) . IEEE Electron Device Lett 36(12):1264. https://doi.org/10.1109/LED.2015.2487563

Johnson RW, Hultqvist A, Bent SF (2014) . Mater Today 17(5):236. https://doi.org/10.1016/j.mattod.2014.04.026

Widiez J, Lolivier J, Vinet M, Poiroux T, Previtali B, Dauge F, Mouis M, Deleonibus S (2005) . IEEE Trans Electron Devices 52(8):1772. https://doi.org/10.1109/TED.2005.851824

(Silvaco Inc) https://silvaco.com

Shockley W, Read WT (1952) . Phys Rev 87:835. https://doi.org/10.1103/PhysRev.87.835

Wang PF, Hilsenbeck K, Nirschl T, Oswald M, Stepper C, Weis M, Schmitt-Landsiedel D, Hansch W (2004) . Solid-state Electron 48:2281

Dharavath Krishna VA (2020) . Silicon 12(6):1391. https://doi.org/10.1007/s12633-019-00232-3

Nibha P, Singh S (2022) . Silicon 14:7017. https://doi.org/10.1007/s12633-021-01476-8

Raj A, Singh S, Priyadarshani KN, Arya R, Naugarhiya A (2021) . Silicon 13(8):2589. https://doi.org/10.1007/s12633-020-00603-1

Kavi KK, Tripathi S (2022) Silicon, pp 1876–9918. https://doi.org/10.1007/s12633-022-01765-w

Saurabh Mookerjea SD, Krishnan R, Narayanan V (2009) . IEEE Electron Device Lett 30:1102. https://doi.org/10.1109/LED.2009.2028907

Suruchi Sharma B.K, Basu R (2021) Silicon. https://doi.org/10.1007/s12633-021-01514-5

Acknowledgements

This work was supported by the SMDP-C2SD under the reference letter no. 9(1)2014-MDD (NIT Delhi, Delhi, India).

Funding

The authors did not receive any financial support from any agency/organization for the submitted work.

Author information

Authors and Affiliations

Contributions

Omendra Kr Singh: Writing original draft preparation, Writing - Reviewing and Editing, Conceptualization, Methodology, and Validation; Vaithiyanathan Dhandapani: Supervision, Validation, Writing - Reviewing and Editing; Baljit Kaur: Supervision, Validation, Writing - Reviewing and Editing.

Corresponding author

Ethics declarations

Ethics approval and consent to participate

The authors declare that they have consent for participation.

Consent for Publication

The authors have consent for the publication of this manuscript.

Competing interests

The authors declare no competing interests.

Conflict of Interests

The authors declare that they have no conflict of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Singh, O.K., Dhandapani, V. & Kaur, B. Partially Extended Germanium Source DG-TFET: Design, Analysis, and Optimization for Enhanced Digital and Analog/RF Parameters. Silicon 15, 1475–1490 (2023). https://doi.org/10.1007/s12633-022-02112-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-02112-9