Abstract

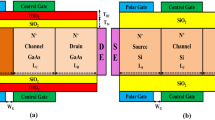

This paper reports on a charged plasma-based adjustable bandgap source/channel (So/Ch) interface using a new semiconductor compound (SiGe/ InAs) and bimaterial oxide (HfO2/SiO2) junctionless tunnel field-effect transistors (JLTFETs). In terms of D.C characteristics, the dual material gate heterogeneous JLTFET (DMG-HJLTFET) outperforms the homogeneous-material Si-JLTFET, with ~ 389 and ~ 3 times greater ION and ION/IOFF, respectively, and ~ 63% lower Vth. At an optimal Ge-mole composition (0.1) of SiGe, the higher output (O/P) is ascribed to the conduction band (C.B) local minima created at the channel, which results in a narrower tunneling barrier width. Furthermore, compared to Si-JLTFET, the DMG-HJLTFET provides 110.5 times greater gm resulting in ~ 1.5 - and 214-times better device efficacy and cut-off frequency (fT), respectively, as well as a ~ 56% drop in the value of parasitic capacitance, promoting it for fast switching applications.

Similar content being viewed by others

Data Availability

Data will be made available on request.

Change history

24 September 2022

A Correction to this paper has been published: https://doi.org/10.1007/s12633-022-02132-5

References

Moore G (1998) Cramming more components onto integrated circuits. Proc of the IEEE, 86, 82–85

Anghel C, Gupta A, Amara A, Vladimirescu A (2011) 30-nm Tunnel FET with improved performance and reduced ambipolar current. IEEE Trans E-Devices 58:1649–1654

Kim JH, Sangwan K, Park BG (2019) Double-Gate TFET with vertical channel sandwiched by lightly doped Si. IEEE Trans E- Devices 66:1656–1661

Shaikh MRU, Loan SA (2019) Drain-engineered TFET with fully suppressed ambipolarity for high-frequency application. IEEE Trans E- Devices 66:1628–1634

Verhulst AS, Vandenberghe WG, Maex K, Gendt SD, Heyns MM, Groeseneken G (2008) Complementary silicon-based heterostructure tunnel-FETs with high tunnel rates. IEEE E- Device Lett 29:1398–1401

Ahn DH, Yoon SH, Kato K, Fukui T, Takenaka M, Takagi S (2019) Effects of ZrO2/Al2O3 gate-stack on the performance of planar-type InGaAs TFET. IEEE Trans E- Devices 66:1862–1867

Avci UE, Young IA (2013) Heterojunction TFET scaling and resonant-TFET for steep subthreshold slope at sub-9nm gate-length. In: Proceedings of the IEEE IEDM, Washington, DC, pp 4.3.1–4.3.4

Singh D, Pandey S, Nigam K, Sharma D, Yadav DS, Kondekar PA (2018) Charge-plasma-based dielectric-modulated Junctionless TFET for biosensor label-free detection. IEEE Trans E- Devices 64:271–278

Aslam M, Sharma D, Yadav S, Soni D, Sharma N, Gedam A (2019) A comparative investigation of low work-function metal implantation in the oxide region for improving electrostatic characteristics of charge plasma TFET. Micro Nano Lett 14:123–128

Haiwu X, Hongxia L, Shupeng C, Tao H, Shulong W (2019) Design and investigation of a dual material gate arsenic alloy heterostructure Junctionless TFET with a lightly doped source. Appl Sci 9:4104

Tao H, Hongxia L, Shupeng C, Shulong W, Wei L (2019) Design and investigation of the high-performance doping-less TFET with Ge/Si0.6Ge0.4/Si heterojunction. Micromachines 10:424

Colinge JP, Lee CW, Afzalian A, Akhavan ND, Yan R, Ferain I et al (2010) Nanowire transistors without junctions. Nat Nanotechnol 5(3):225–229. https://doi.org/10.1038/nnano.2010.15

Lee CW, Afzalian A, Akhavan ND, Yan R, Ferain I, Colinge JP (2009) Junctionless multigate field-effect transistor. Appl Phys Lett 94(5):053511. https://doi.org/10.1063/1.3079411

Djeffal F, Ferhati H, Bentrcia T (2016) Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattices Microstruct 1(90):132–140

Kumar MJ, Janardhanan S (2013) Dopingless tunnel field-effect transistor: design and investigation. IEEE Trans E- Devices 60(10):3285–3290

Ghosh B, Akram MW (2013) Junctionless tunnel field-effect transistor. IEEE E- Device Lett 34(5):584–586

Seabaugh AC, Zhang Q (2010) Low voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98(12):2095–2110

Xie H, Liu H, Wang S, Chen S, Han T, Li W (2019) Improvement of electrical performance in heterostructure junctionless TFET based on dual material gate. Appl Sci 2020(10)126. https://doi.org/10.3390/app10010126

Sharma S, Chaujar R (2020) Performance analysis of a novel hetero-material InAs/GaAs junctionless TFET. In: 2020 IEEE VLSI device circuit and system (VLSI DCS). IEEE, p 38–41

Asthana PK, Ghosh B, Goswami Y, Tripathi BMM (2014) High-speed and low-power ultradeep-submicrometer III-V hetero junctionless tunnel field-effect transistor. IEEE Trans E- Devices 61(2):479–486

Vadizadeh M (2018) Characteristics of GaAs/GaSb tunnel field-effect transistors without doping junctions: numerical studies. J Comput E- 17(2):745–755

Ferhati H, Djeffal F, Bentrcia T (2018) The role of the Ge mole composition in improving the performance of a nanoscale junctionless tunneling FET: concept and scaling capability. Beilstein J Nanotechnol 9(1):1856–1862

Sharma S, Chaujar R (2021) Band gap and gate metal engineering of novel hetero-material InAs/GaAs-based JLTFET for improved wireless applications. J Mater Sci: Mater E- 32(3):3155–3166. https://doi.org/10.1007/s10854-020-05064-1

Li R et al (2012) AlGaSb/InAs tunnel field-effect transistor with on-current of 78 uA/um at 0.5 V. IEEE Electron Device Lett 33(3):363–365. https://doi.org/10.1109/LED.2011.2179915

Panda S, Dash S (2022) Drain dielectric pocket engineering: its impact on the electrical performance of a hetero- structure tunnel FET. Silicon. https://doi.org/10.1007/s12633-022-01707-6

Vadizadeh M (2021) Digital performance assessment of the dual-material gate GaAs/InAs/Ge Junctionless TFET. IEEE Trans E- Devices 68:4

Silvaco Atlas user’s manual (2018) [Online]. Available: http://www.silvaco.com

Hansch W, Vogelsang Th, Kircher R, Orlowski M (1989) Carrier transport near the Si/ SiO2 interface of a MOSFET. Solid-State Electron 32(10):839–849

Zhao Y, Wu C, Huang Q, Chen C, Zhu J, Guo L et al (2017) A novel tunnel FET design through adaptive bandgap engineering with constant sub-threshold slope over 5 decades of current and high ION/IOFF ratio. IEEE E- Device Lett 38(5):540–543

Wang CH, Chu H, Lai YS et al (2008) Dual work-function metal gates, vol 73. US Patent, p 81619B2

Johnson RW, Hultqvist A, Bent SF (2014) A brief review of atomic layer deposition: from fundamentals to applications. Mater Today 17(5):236–246

Samriti S, Rishu C (2021) Performance enhancement in a novel amalgamation of arsenide/antimonide tunnelling interface with charge plasma junctionless-TFET. Int J E- Commun (AEU) 133(2021):153669

Mamidala JK, Vishnoi R, Pandey P (2016) Tunnel field-effect transistors (TFET) modeling and simulations. Wiley, Hoboken

Kumar A, Gupta A, Tripathi MM, Chaujar R (2019) RF Noise Modeling of Black Phosphorus Junctionless Trench MOSFET in Strong Inversion Region. Superlattices Microstruct 125:72–79. https://doi.org/10.1016/j.spmi.2018.10.025

Afreen AH, Varun M, Yogesh KV, Santosh KG (2022) Investigation of novel low bandgap source material for heterodielectric GAATFET with enhanced performance. Silicon. https://doi.org/10.1007/s12633-021-01571-w

Acknowledgements

Authors would like to thank the Indian Institute of Technology, Roorkee, and Graphic Era (Deemed to be University) for their support and permission to communicate this research paper.

Author information

Authors and Affiliations

Contributions

Kaushal Kumar (first and corresponding author) conceived the research study and wrote the paper.

Ajay Kumar planned the study, reviewed and corrected the manuscript.

Varun Mishra planned the study, reviewed and corrected the manuscript.

Subhash Chandra Sharma, planned the study and preparation of figures, and reviewed and corrected the manuscript.

Corresponding author

Ethics declarations

Ethics Approval

Not applicable (as the results of studies do not involve any human or animal).

Consent to Participate

Not applicable (as the results of studies do not involve any human or animal).

Consent for Publication

Yes.

Conflict of Interest

The authors declare that they have no conflicts of interest.

Research Involving Human Participants and/or Animals

Not Applicable (as the results of studies do not involve any human or animal).

Informed Consent

All authors read and approved the final manuscript.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, K., Kumar, A., Mishra, V. et al. Implementation of Band Gap and Gate Oxide Engineering to Improve the Electrical Performance of SiGe/InAs Charged Plasma-Based Junctionless-TFET. Silicon 15, 1303–1313 (2023). https://doi.org/10.1007/s12633-022-02111-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-02111-w