Abstract

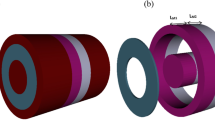

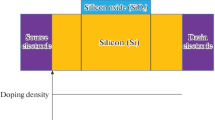

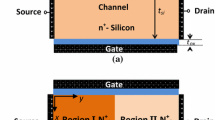

This paper presents Gate Stacked junctionless nanotube gate all around MOSFET (GS JL NT GAA MOSFET) and its investigation for low power circuit applications. In GS architecture, high-k material as dielectrics was placed over SiO2 which is deposited around the silicon nanotube (for inner and outer surface of silicon nanotube). GS JL NT GAA MOSFET is also compared with non-stacked junctionless nanotube (JL-NT MOSFET) for performance analysis. GS JL NT GAA MOSFET provides a reduced leakage current (~10−16) and high ION/IOFF ratio (~1011) as compared to non-stacked device. Side spacer of suitable material needs to be selected for enhancing the performance metrics such as ION/IOFF ratio, SS, DIBL. Furthermore, the spacer length and diameter of core gate also plays vital role for device design. Therefore, GS JL NT GAA MOSFET has low leakage and high switching speed, which leads it for low power circuit applications.

Similar content being viewed by others

Data Availability

The research data of this manuscript will not be available.

References

Colinge JP, Lee CW, Akhavan ND, Yan R, Ferain I, Razavi P … Yu R (2011) Junctionless transistors: physics and properties. Semiconductor-on-insulator materials for nanoelectronics applications. Springer, Berlin, pp 187–200

Colinge JP et al (2010) Nanowire transistors without junctions. Nature Nanotechnol 5(3):225–229

Lee CW, Afzalian A, Akhavan ND, Yan R, Ferain I, Colinge JP (2009) Junctionless multigate field-effect transistor. Appl Phys Lett 94(5):053511

Choi SJ, Moon DI, Kim S, Duarte JP, Choi YK (2010) Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. IEEE Electron Device Lett 32(2):125–127

Gundapaneni S, Bajaj M, Pandey RK, Murali KV, Ganguly S, Kottantharayil A (2012) Effect of band-to-band tunneling on junctionless transistors. IEEE Trans Electron Devices 59(4):1023–1029

Doria RT et al (2011) Junctionless multiple-gate transistors for analog applications. IEEE Trans Electron Devices 58(8):2511–2519

Gnudi A, Reggiani S, Gnani E, Baccarani G (2013) Semianalytical model of the subthreshold current in short-channel junctionless symmetric double-gate field-effect transistors. IEEE Trans Electron Devices 60(4):1342–1348

Kumari V, Modi N, Saxena M, Gupta M (2015) Modeling and simulation of double gate junctionless transistor considering fringing field effects. Solid State Electron 107:20–29

Hu G, Xiang P, Ding Z, Liu R, Wang L, Tang T-A (2014) Analytical models for electric potential, threshold voltage, and subthreshold swing of junctionless surrounding-gate transistors. IEEE Trans Electron Devices 61(3):688–695

Bala S, Khosla M (2019) Design and performance analysis of low power SRAM based on electrostatic doped tunnel-CNTFET. J Comput Electron 18(3):856–863

Sahay S, Kumar MJ (2017) Diameter dependence of leakage current in nanowire junctionless field effect transistors. IEEE Trans Electron Devices 64(3):1330–1335

Fan J, Li M, Xu X, Yang Y, Xuan H, Huang R (2015) Insight into gate-induced drain leakage in silicon nanowire transistors. IEEE Trans Electron Devices 62(1):213–219

Hur J et al (2016) Comprehensive analysis of gate-induced drain leakage in vertically stacked nanowire FETs: inversion-mode versus junctionless mode. IEEE Electron Device Lett 37(5):541–544

Fahad HM, Smith CE, Rojas JP, Hussain MM (2011) Silicon nanotube field effect transistor with core–shell gate stacks for enhanced high-performance operation and area scaling benefits. Nano Lett 11(10):4393–4399

Kumar R, Bala S, Kumar A (2021) Analytical modelling and simulation analysis of junctionless nanotube (JL NT) MOSFET. Trans Electr Electron Mater:1–9

Tekleab D, Tran HH, Sleight JW, Chidambarrao D (2012) Silicon nanotube MOSFET, U.S. Patent 0 217 468

Tiwari PK, Samoju VR, Sunkara T, Dubey S, Jit S (2016) Analytical modeling of threshold voltage for symmetrical silicon nano-tube field-effect-transistors (Si-NT FETs). J Comput Electron 15(2):516–524

Kumar A, Bhushan S, Tiwari PK (2017) Analytical modeling of subthreshold characteristics of ultra-thin double gate-all-around (DGAA) MOSFETs incorporating quantum confinement effects. Superlattice Microst 109:567–578

Kumar A, Tiwari PK (2018) An explicit unified drain current model for silicon-nanotube-based ultrathin double gate-all-around mosfet s. IEEE Trans Nanotechnol 17(6):1224–1234

Sahay S, Kumar MJ (2017) Nanotube junctionless FET: proposal, design, and investigation. IEEE Trans Electron Devices 64(4):1851–1856

Rewari S, Haldar S, Nath V, Deswal SS, Gupta RS (2016) Numerical modeling of subthreshold region of junctionless double surrounding gate MOSFET (JLDSG). Superlattice Microst 90:8–19

Tayal S, Nandi A (2018) Optimization of gate-stack in junctionless Si-nanotube FET for analog/RF applications. Mater Sci Semicond Process 80:63–67

Rewari S, Nath V, Haldar S, Deswal SS, Gupta RS (2019) Hafnium oxide based cylindrical junctionless double surrounding gate (CJLDSG) MOSFET for high speed, high frequency digital and analog applications. Microsyst Technol 25(5):1527–1536

Kumar R, Bala S, Kumar A (2021) Study and analysis of advanced 3D multi-gate junctionless transistors. Silicon PP:1–15

Suzuki K, Tanaka T, Tosaka Y, Horie H, Arimoto Y (1993) Scaling theory for double-gate SOI MOSFET’s. IEEE Trans Electron Devices 40(12):2326–2329

Sasaki H, Ono M, Yoshitomi T, Ohguro T, Nakamura SI, Saito M, Iwai H (1996) 1.5 nm direct-tunneling gate oxide Si MOSFET’s. IEEE Trans Electron Devices 43(8):1233–1242

Baidya A, Baishya S, Lenka TR (2017) Impact of thin high-k dielectrics and gate metals on RF characteristics of 3D double gate junctionless transistor. Mater Sci Semicond Process 71:413–420

Narendar V, Mishra RA (2015) Analytical modeling and simulation of multigateFinFET devices and the impact of high-k dielectrics on short channel effects (SCEs). Superlattice Microst 85:357–369

Ghosh P, Haldar S, Gupta RS, Gupta M (2012) Analytical modeling and simulation for dual metal gate stack architecture (DMGSA) cylindrical/surrounded gate MOSFET. J Semicond Technol Sci 12(4):458–466

Singh S, Raman A (2018) Gate-all-around charge plasma-based dual material gate-stack nanowire FET for enhanced analog performance. IEEE Trans Electron Devices 65(7):3026–3032

Darwin S, Samuel TA (2020) A holistic approach on Junctionless dual material double gate (DMDG) MOSFET with high k gate stack for low power digital applications. Silicon 12(2):393–403

Atuchin VV, Lebedev MS, Korolkov IV, Kruchinin VN, Maksimovskii EA, Trubin SV (2019) Composition-sensitive growth kinetics and dispersive optical properties of thin Hf x Ti 1− x O 2 (0≤ x≤ 1) films prepared by the ALD method. J Mater Sci Mater Electron 30(1):812–823

He G, Liu J, Chen H, Liu Y, Sun Z, Chen X, Liu M, Zhang L (2014) Interface control and modification of band alignment and electrical properties of HfTiO/GaAs gate stacks by nitrogen incorporation. J Mater Chem C 2(27):5299–5308

Reference manual, Genius, 3-D Device Simulator, Version 1.9.2-3. Cogenda Pvt. Ltd, Singapore, 2017

Singhal T, Singhal A, Chawla S, Bhatia V (2021) Design and simulation of charge transport in single-electron transistor using TCAD numerical simulator. Chin J Phys

Acknowledgments

Raj Kumar acknowledges the UGC, India for the financial assistance and UIET (ECE), Panjab University for providing Lab facility.

Author information

Authors and Affiliations

Contributions

All the authors have contributed in framing, writing and proofreading the manuscript.

Corresponding author

Ethics declarations

This article does not contain any studies involving animals or human participants performed by any of the authors.

Consent to Participate

Not Applicable.

Consent for Publication

Not Applicable.

Ethics Approval

Not Applicable.

Conflict of Interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Bala, S., Kumar, R., Hrisheekesha, P.N. et al. Gate Stacked (GS) Junctionless Nanotube MOSFET: Design and Analysis. Silicon 15, 1037–1047 (2023). https://doi.org/10.1007/s12633-022-02071-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-02071-1