Abstract

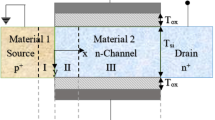

A two-dimensional analytical model is proposed in this paper for surface potential and drain current on Triple Material Surrounding Gate Heterojunction Tunnel Field Effect Transistor (HJ-TFET). The theoretical analysis is performed to break down the 2D Poisson Equations into two 1D equations. By implementing Finite Differentiation Method and varying work functions, Triple Material Gates are decomposed into three different individual gates with different work functions. These individual 1D Poisson equations that are decomposed are combined by applying sufficient boundary constraints. As a result, this reduces the difficulty of solving 2D Poisson equations. The expressions of surface potential and drain current are made simpler for the proposed analytical model. Finally, the outcomes of the study are correlated with the TCAD simulation. The proposed model is therefore validated to explain the nature of the Triple Material Surrounding Gate Heterojunction TFETs.

Similar content being viewed by others

Code Availability

Not Applicable.

References

Saurabh, S., Jagadesh Kumar, M.: Fundamentals of tunnel field-effect transistors, India (2016)

Colinge, J.-P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.-M., Mc Carthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan R., Ferain, I., Colinge, J.-P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett 2(5), 053511-1–053511-2 (2009)

Colinge, J.P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., Dehdashti Akhavan, N., Razavi, P.: Junctionless nanowire transistor (JNT): Properties and design guidelines. Solid State Electron. 65-66, 33–37 (2011)

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans. Electron. Devices 54(7), 1725–1733 (2007)

Mitra, S.K., Goswami, R., Bhowmick, B.: A hetero-dielectric stack gate SOI-TFET with back gate and its application as a digital inverter. Superlattices Microstruct. 92:37–51 (2016)

Kumar, S., Goel, E., Singh, K., Singh, B., Kumar, M., Jit, S.: A compact 2-D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a SiO2/high- k stacked gate-oxide structure. IEEE Trans. Electron. Devices 63(8), 3291–3299 (2016)

Gandhi, R., Chen, Z., Singh, N., Banerjee, K., Lee, S.: Vertical Si-nanowire n-Type tunneling FETs with low subthreshold swing (≤50 mV/decade) at room temperature. IEEE Electron. Device Lett. 32(4), 437–439 (2011)

Mallik, A., Chattopadhyay, A.: Impact of a spacer dielectric and a gate overlap/underlap on the device performance of a tunnel field-effect transistor. IEEE Trans. Electron Devices 58(3), 677–683 (2011).

Taur, Y., Ning, T.H.: Fundamentals of modern VLSI devices. Cambridge University Press (2013)

Guan, Y., Li, Z., Zhang, W., Zhang, Y.: An accurate analytical current model of double-gate heterojunction tunneling FET. IEEE Trans. Electron Devices 64(3), 938–944 (2017)

Jaya Madan, R.S., Chaujar, G.R.: Mathematical modeling insight of hetero gate dielectric-dual material gate-GAA-tunnel FET for VLSI/analog application. Microsyst. Technol. 234, 4091–4098 (2016)

Gupta, S.K., Kumar, S.: Analytical modeling of a triple material double gate TFET with hetero-dielectric gate stack. Silicon 114, 1355–1369 (2019)

Knoch, J.: Optimizing tunnel FET performance—Impact of device structure, transistor dimensions and choice of material. Proc. Int. Symp. VLSI-TSA: 45–46 (2009)

Toh, E.-H., Wang, G.H., Samudra, G., Yeo, Y.-C.: Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high-performance applications. J. Appl. Phys. 103(10), 104504 (2008)

Brouzet, V., Salem, B., Periwal, P., Alcotte, R., Chouchane, F., Bassani, F., Baron, T., Ghibaudo, G.: Fabrication and electrical characterization of homo- and hetero-structure Si/SiGe nanowire tunnel field effect transistor grown by vapor–liquid–solid mechanism. Solid-State Electron. 118, 26–29 (2016)

Dong, Y., Zhang, L., Li, X., Lin, X., Chan, M.: A compact model for double-gate heterojunction tunnel FETs. IEEE Trans. Electron. Devices 63(11), 4506-4513 (2016)

Troutman, R.R.: VLSI limitations from drain-induced barrier lowering. IEEE Trans. Electron Devices 26(4), 461–469 (1979)

Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J. K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Toh, E.-H., Wang, G.H., Chan, L., Samudra, G., Yeo, Y.-C.: Device physics and guiding principles for the design of double-gate tunnelling field effect transistor with silicon-germanium source heterojunction. Appl Phys. Lett. 91, 243505 (2007)

Krishnamohan, T., Kim, D., Raghunathan, S., Saraswat, K.: Doublegate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and < 60 mV/dec subthreshold slope. IEEE International Electron Devices Meeting (IEDM), pp 1–3 (2008)

Usha, C., Vimala, P., Samuel, T.S.A. et al.: A novel 2-D analytical model for the electrical characteristics of a gate-all-around heterojunction tunnel field-effect transistor including depletion regions. J. Comput. Electron. 19, 1144–1153 (2020)

Usha, C., Vimala, P.: An electrostatic analytical modeling of high-k stacked gate-all-around heterojunction tunnel FETs considering the depletion regions. Int. J. Electron. Commun. (2019)

Usha, C., Vimala, P., Samuel, T.S.A. et al.: A novel 2-D analytical model for the electrical characteristics of a gate-all-around heterojunction tunnel field-effect transistor including depletion regions. J. Comput. Electron. 19, 1144–1153 (2020)

Manikandan, S., Balamurugan, N.B., Nirmal, D.: Analytical model of double gate stacked oxide junctionless transistor considering source/drain depletion effects for CMOS low power applications. Silicon 12, 2053–2063 (2020)

Xu, H.F., Guan, B.G.: Two-dimensional analytical model for hetero-junction double-gate tunnel field-effect transistor with a stacked gate-oxide structure. Japanese Journal of Applied Physics (JJAP) 56(5), 054201 (2017)

Kumar, S. et al.: 2-D analytical drain current model of double-gate heterojunction TFETs with a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices 65(1), 331-338 (2018)

Tiwari, P.K., Dubey, S., Singh, K., Jit, S.: Analytical modeling of sub-threshold current and sub-threshold swing of short-channel triple material double-gate (TM-DG) MOSFETs. Superlattices and Microstruct 51, 715–724 (2012)

Suveetha Dhanaselvam, P., Balamurugan, N.B., Ramakrishnan, V.N.: A 2D Transconductance and Sub-threshold behavior model for triple material surrounding gate (TMSG) MOSFETs, Microelectronics Journal 44(12), 1159–1164 (2013)

Wang, H.K., Wu, S., Chiang, T.K., Lee, M.S.:A new two-dimensional analytical threshold voltage model for short-channel triple-material surrounding-gate metal oxide-semiconductor field-effect transistors. J. Appl. Phys. 51, 054301 (2012)

Acknowledgements

The authors are grateful to the Management of “Thiagarajar college of Engineering”, Madurai for the support extended to carry out this research work.

Funding

No funding was received to assist with the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

Review and editing, Support for simulation work- [Dr.M.Suguna].

Draft preparation- [V. A Nithya sree], [R.Kaveri]

Draft preparation-[M.Hemalatha].

Idea of the article, resources, Supervision-[Dr.N.B.Balamurugan].

Result and validation – [Dr.D.Sriram kumar], [Dr.P.Suveetha Dhanaselvam].

Corresponding author

Ethics declarations

CONFLICTS OF INTEREST/COMPETING INTERESTS

The authors have no relevant financial or nonfinancial interests to disclose.

ETHICS APPROVAL AND CONSENT TO PARTICIPATE

All authors freely agreed and gave their consent for the publication of this paper.

CONSENT FOR PUBLICATION

All authors freely agreed and gave their consent for the publication of this paper.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic Supplementary Material

Below is the link to the electronic supplementary material.

Rights and permissions

About this article

Cite this article

Suguna, M., Nithya sree, V.A., Kaveri, R. et al. Analytical modeling and Simulation Based Investigation of Triple material surrounding gate heterojunction tunnel FET. Silicon 14, 10729–10740 (2022). https://doi.org/10.1007/s12633-022-01687-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01687-7