Abstract

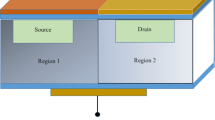

In this study, an accurate model for threshold voltage of graded channel dual material double gate (GCDMDG) structure metal-oxide-semiconductor (MOS) has been established and a comparative explored by using SiO2 as well as HfO2 materials. The threshold voltage roll-off and drain-induced-barrier-lowering (DIBL) have been explored. The effect of different device parameters like temperature, oxide thickness, film thickness, etc. on device performance has been evaluated to check the figure of merit over the DMDG structure. It is found that the value of threshold voltage is higher in GCDMDG structure over its counterpart but the roll-off nature is quite small. The main purpose is to reduce the short channel effects (SCEs), that has been generated due to the miniaturization of the device. For the confirmation of the model, the results have been affirmed by TCAD.

Similar content being viewed by others

References

Nicollian, E. H. and Brews, J. R. (2002). MOS (metal oxide semiconductor) physics and technology. Wiley

Neamen, D. (2017). Semiconductor physics and devices. McGraw Hill

Cerdeira A, Moldovan O, Iñiguez B, Estrada M (2008) Modeling of potentials and threshold voltage for symmetric doped double gate MOSFETs. Solid State Electron 52:830–837

Suzuki K (1995) Analytical models for n+-p+ double gate SOI MOSFET’s. IEEE Trans. on Electron. Devices 42(11):1940–1947

Chakrabarti H, Maity R, Baishya S, Maity NP (2020) An accurate model for threshold voltage analysis of dual material double gate metal oxide semiconductor field effect transistor. Silicon. 13:1851–1861. https://doi.org/10.1007/s12633-020-00553-8

Kumar MJ, Chaudhury A (2004) Two-dimensional analytical modelling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans on Electron Devices 51(4):569–574

Kumar MJ, and. Reddy, G. V. (2004) Evidence for suppressed short-channel effects in deep submicron dual-material gate (DMG) partially depleted SOI MOSFETs-A two dimensional analytical approach. Microelectron Eng 75:367–374

Maity NP, Maity R, Thapa RK, Baishya S (2015) Effect of image force on tunneling current for ultra thin oxide layer based metal oxide semiconductor devices. Nanosci Nanotechnol Lett 7(4):331–333

Chiang TK (2016) A short channel effect degraded noise margin model for junctionless double gate MOSFET working on subthreshold CMOS logic gates. IEEE Trans. Electron. Devices 63(8):3354–3359

Chaudhury, A and Kumar, M. J. (2004). Investigation of the novel attributes of a fully depleted dual material gate SOI MOSFET. IEEE Trans. on Electron. Devices, vol. 51, no. 9, pp. 1463–1467

Reddy GV, Kumar MJ (2005) A new dual-material double-gate (DMDG) nanoscale SOI MOSFET-two-dimensional analytical modeling and simulation. IEEE Trans. on Nanotechnol 4(2):260–268

Chakrabarti H, Maity R, Maity NP (2019) Analysis of surface potential for dual-material-double-gate MOSFET based on modelling and simulation. Microsyst Technol 25:4675–4684

Maity NP, Maity R, Maity S, Baishya S (2019) Comparative analysis of the quantum FinFET and Trigate FinFET based on modeling and simulation. J Comput Electron 18(2):492–499

Goel E, Kumar S, Singh K, Singh B, Kumar M (2016) 2-D analytical Modelling of threshold voltage for Graded-Channel dual-material double-gate MOSFETs. IEEE Trans Electron Devices 63(3):966–973

Chakrabarti H, Maity R, Kevkić T, Stojanović V, Maity NP (2020) Analysis of surface potential and electric field for fully depleted Graded Channel dual-material-double-gate MOSFET through modeling and simulation. Trans Electr Electron Mater 22:489–501. https://doi.org/10.1007/s42341-020-00256-2

Kaur H, Kabra S, Haldar S, Gupta RS (2008) An analytical threshold voltage model for graded channel asymmetric gate stack (GCASYMGAS) surrounding gate MOSFET. Solid State Electron 52:305–311

Narendar V, Girdhardas KA (2018) Surface potential modeling of Graded-Channel Gate-Stack (GCGS) High-K Dielectric Dual-Material Double-Gate (DMDG) MOSFET and Analog/RF Performance Study. Silicon 10:2865–2875

Maity NP, Maity R, Baishya S (2019) An analytical model for the surface potential and threshold voltage of a double gate Heterojunction tunnel FinFET. J Comput Electron 18(1):65–75

Maity NP, Maity R, Baishya S (2019) A new surface potential and drain current model of dual material gate Short Channel metal oxide semiconductor field effect transistor in sub-threshold regime: application to high-k material HfO2. J of Nanoelectronics & Optoelectronics 14:868–876

Jelodar MS, Ilatikhameneh H, Kim S, Ng K, Klimeck G (2016) Optimum high-k oxide for the best performance of ultrascaled double-gate MOSFETs. IEEE Trans on Nanotechnol 15:904–910

Chaudhry A, Kumar MJ (2004) Controlling short-channel effects in deep submicron SOI MOSFETs for improved reliability: a review. IEEE Trans on Device and Materials Reliability 4:99–109

Jeong S, Bae I, Shin Y, Lee S, Kwak H, Boo J (2005) Physical and electrical properties of ZrO2 and YSZ high-k gate dielectric thin films grown by RF magnetron sputtering. Thin Solid Films 475:354–358

Miyoshi J, Diniz J, Barros A, Doi I, Von Zuben A (2010) Titanium–aluminum oxynitride (TAON) as high-k gate dielectric for sub-32 nm CMOS technology. Microelectron Eng 87:267–270

Noor FA, Abdullah M, Khairurrijal S, Ohta A, Miyazaki S (2010) Electron and hole components of tunneling currents through an interface.al oxide-high-k gate stack in metal-oxide-semiconductor capacitors. Journal of Applied Physics 108:093711

Robertson J (2004) High dielectric constant oxides. Eur Phys Journal Applied Physics 28:265–291

Fu C, Liao K, Liu L, Li C, Chen T, Cheng J, Lu C (2014) An ultralow EOT Ge MOS device with tetragonal HfO2 and high quality HfXGeYO interfacial layer. IEEE Trans on Electron Devices 61:2662–2667

Ganapathi KL, Bhattacharjee S, Mohan S, Bhat N (2016) High performance HfO2 Back gated multilayer MoS2 transistor. IEEE Electron Device Letters 37:797–800

Maity NP, Maity R, Baishya S (2018) A tunneling current model with a realistic barrier for UltraThin high-k dielectric ZrO2 material based MOS devices. Silicon 10:1645–1652

Panchanan S, Maity R, Baishya S, Maity NP (2021) A surface potential model for tri-gate metal oxide semiconductor field effect transistor: analysis below 10 nm channel length. Engineering Science and Technology, an International Journal 24:879–889

Panchanan, S., Maity, R., Baishya, S., Maity, N. P. (2021). Modeling, simulation and analysis of surface potential and threshold voltage: application to high-k material HfO2 based FinFET. Silicon, https://doi.org/10.1007/s12633-020-00607-x, online published on 20th October, 2020

Maity, N. P., Thakkur, R. R., Maity, R., Thapa, R. K., Baishya, S. (2016). Analysis of Interface Charge Densities for High-k Dielectric Materials based Metal-Oxide-Semiconductor Devices. International Journal of Nanoscience, Vol. 15, No. 3, 1660011 1–6, 2016

Sochacki M, Krol K, Waskiewicz M, Racka K, Szmidt J (2016) Interface traps in Al/HfO2/SiO2/4H-SiC metal-insulator-semiconductor (MIS) structures studied by the thermally-stimulated current (TSC) technique. Microelctronic Engineering 157:46–51

Maity NP, Maity R, Thapa RK, Baishya S (2016) A tunneling current density model for ultra thin HfO2 high-k dielectric material based MOS devices. Superlattice Microst 95:24–32

Shanfield Z, Brown G, Revesz A, Hughes H (2002) A new MOS radiation-induced charge: negative fixed Interface charge. IEEE Trans Nucl Sci 39:303–307

Maity, N. P., Maity, R., Dutta, S., Deb, S., Saravani, K.G., Rao, K. S., and Baishya, S. (2020). Effects of hafnium oxide on surface potential and drain current models for subthreshold Short Channel metal-oxide-Semoconductor-field-effect-transistor. Transactions on electrical and electronic materials. Online published on 23rd Feb., 2020, DOI: https://doi.org/10.1007/s42341-020-00181-4, 21, 339, 347

Srinivasan V, Pandya A (2011) Dosimetry aspects of hafnium oxide metal-oxide-semiconductor (MOS) capacitor. Thin Solid Films 520:574–577

Tapajna M, Huseková K, Espinos JP, Harmatha L, Fröhlich K (2006) Precise deter-mination of metal effective work function and fixed oxide charge in MOS capacitors with high dielectric. Material Science Semiconductor Processing 9:969–974

Litta E, Hellstrom P, Ostling M (2015) Threshold voltage control in TmSiO/HfO2 high-k/metal gate MOSFETs. Solid State Electronics 108:24–29

Narang R, Saxena M, Gupta RS, Gupta M (2013) Impact of temperature variations on the device and circuit performance of tunnel FET: a simulation study. IEEE Trans Nanotechnol 12(6):951–957

Acknowledgements

The Authors are highly indebted to National Institute of Technology, Silchar, and Mizoram University (A Central University), Aizawl for supporting this technical work.

Availability of Data and Material

Not Applicable.

Funding

No direct funding was received to assist with the work of this manuscript.

Author information

Authors and Affiliations

Contributions

All authors contributed to the study conception and design. All authors approve the manuscript.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

We comply with the ethical standards of this journal.

Disclosure of Potential Conflicts of Interest

There is no Conflict of Interest or Competing Interests for the work.

Informed Consent

This research did not involve any human subjects. The authors provide consent for their research work.

Consent for Publication

The Authors hereby agree to publish this manuscript in Journal of Silicon. The manuscript has not been submitted or published any other Journal.

Consent to Participate

All the authors have made substantial contributions toward the final draft of the paper.

Research Involving Human Participants and/or Animals

This work does not contain any studies with human participants or animals performed by any of the authors.

Conflicts of Interest/Competing Interests

The authors state that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Chakrabarti, H., Maity, R., Baishya, S. et al. An Accurate Model of Threshold Voltage and Effect of High-K Material for Fully Depleted Graded Channel DMDG MOSFET. Silicon 14, 9763–9772 (2022). https://doi.org/10.1007/s12633-021-01412-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01412-w