Abstract

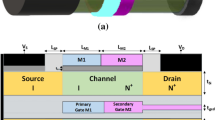

In present work, a Linearly Graded (LG) work function is studied by considering the binary metal alloy AσB1−σ composition for the gate electrode. A high-k gate stack LG nanotube field-effect transistor (LG-NT-FET) is investigated for improving the analog performance and reduced leakage current. The present paper introduces novelty by adding charge plasma on the drain side while doping the source side in LG-NT-FET. The proposed device has the core gate, which lays inside the channel and drain area. Both the gates, including the inner and outer gates are playing a crucial role to significantly charge the channel of LG-NT-FET. It can significantly reduce the Short Channel Effects (SCEs) also. Evaluating the electrical performance metrics such as drive currents and SCEs of LG-NT-FET reveals that the proposed device can better perform in comparison with single gate silicon-based nanotube field-effect transistors (SG-NT-FETs). The device metrics get further enhanced with the tightened electrostatic control via stacking of the core-shell gate that enabled volume inversion-phase operation. The comparison of the LG-NT-FET with single gate NTFET offered a significant reduction in leakage current (~ 10− 15), rise in \({\boldsymbol{I}}_{\boldsymbol{O}\boldsymbol{N}}/{\boldsymbol{I}}_{\boldsymbol{O}\boldsymbol{F}\boldsymbol{F}}\) ratio (~ 1013), increase in transconductance and cutoff frequency as compared to the single gate SG-NT-FET. These improvements in electrical performance metrics enable the proposed device, LG-NT-FET, as a potential device to enable CMOS scaling criteria beyond the Si-NW-FET. These improvised characteristics make LG-NT-FET a promising device in designing both digitals and analog applications for FETs.

Similar content being viewed by others

Data Availability

Not applicable.

Code Availability

Not applicable.

References

Nagy D, Indalecio G, Garcia-Loureiro AJ, Elmessary MA, Kalna K, Seoane N (2018) FinFET versus gate-all-around nanowire FET: performance, scaling, and variability. IEEE J Electron Devices Soc 6(1):332–340

Jain A, Sharma S, Raj B (2016) Design and analysis of high sensitivity Photosensor using cylindrical surrounding gate MOSFET for low power sensor applications. Eng Sci Technol, Elsevier’s 19(4):1864–1870

Choi SJ, Moon DI, Kim S, Duarte JP, Choi YK (2010) Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. IEEE Electron Device Lett 32(2):125–127

Sharma SK, Raj B, Khosla M (2016) A Gaussian approach for analytical subthreshold current model of cylindrical nanowire FET with quantum mechanical effects. Microelectron J 53:65–72

Girish Wadhwa B, Raj (2019) Design, simulation and performance analysis of JLTFET biosensor for high sensitivity. IEEE Trans Nanotechnol 18:567–574. https://doi.org/10.1109/TNANO.2019.2918192

Kumar A, Bhushan S, Tiwari PK (2017) A threshold voltage model of silicon-nanotube-based ultrathin double gate-all-around(DGAA) MOSFETs incorporating quantum confnement efects. IEEE Trans Nanotechnol 16(5):868–875

Wadhwa G, Raj B (2018) Parametric variation analysis of symmetric double gate charge plasma JLTFET for biosensor application. IEEE Sens J 18(15):6070–6077

Manna B, Sarkhel S, Islam N, Sarkar S, Sarkar SK (2012) Spatial composition grading of binary metal alloy gate electrode for short-channelSOI/SON MOSFET application. IEEE Trans Electron Devices 59(12):3280–3287

Tsui BY, Huang CF (2003) Wide range work function modulation of binary alloys for MOSFET application. IEEE Electron Device Lett 24(3):153–155

Yu B, Yuan Y, Song J, Taur Y (2009) A two-dimensional analytical solution for short-channel effects in nanowire MOSFETs. IEEE Trans Electron Devices 56(10):2357e2362

Deb S, Singh NB, Islam N, Sarkar SK (2011) Work function engineering with linearly graded binary metal alloy gate electrode for short-channel SOI MOSFET. IEEE Trans Nanotechnol 11(3):472–478

Wadhera T, Wadhwa G, Bhardwaj TK, Kakkar D, Raj B (2020) Design and performance analysis of symmetrical and asymmetrical triple gate dopingless vertical TFET for biorecognition. Silicon :1–9

Chakraborty AMallikS, Sarkar CK (2008) Subthreshold performance of dual-material gate CMOS devices and circuits for ultralow-poweranalog/mixed-signal applications. IEEE Trans Electron Device 55(3):827–832

Sahay S, Kumar MJ (2017) Nanotube junctionless FET: proposal, design, and investigation. IEEE Trans Electron Devices 64(4):1851–1856

Singh S, Yadav S, Rahul J, Srivastava A, Raj B (2015) Impact of HfO2 in Graded Channel dual insulator double gate MOSFET. J Comput Theor Nanosci, American Scientific Publishers 12(6):950–953

Farkhanda Ana D. Najeeb-Ud-Din(2012) Optimisation of metal gate work function engineering for the deep sub-micron MOSFET’s. IJECT 3(4):2230e7109

Awanit Sharma S, Akash (2013) Performance analysis of gate-all-aroundfield-effect transistor for CMOS nanoscale devices. Int J Comput Appl 84(10):975e8887

Sharma D, Vishvakarma SK (2015) Analyses of DC and analog/RF performances for short channel quadruple-gategate-all-around MOSFET. Microelectron J 46(8):731–739

Fahad HM, Hussain MM (2012) Are nanotube architectures more advantageous than nanowire architectures for field effect transistors? Sci Rep 2:475

Bagga N, Sarkhel S, Sarkar SK (2016) Exploring the Asymmetric Characteristics of a Double Gate MOSFET with Linearly Graded Binary Metal Alloy Gate Electrode for Enhanced Performance. IETE J Res 62(6):786–794

Tayal S, Nandi A (2017)Analog/RF performance analysis of inner gate engineered junctionless Si nanotube. Superlattice Microst 111:862–871

Shan C, Wang Y, Bao MT (2016) A charge-plasma-based transistor with induced Graded Channel for enhanced analog performance. IEEE Trans Electron Devices 63(6):2275–2281

(2004) ATLAS User’s Manual Device simulation software

Gundapaneni S, Ganguly S, Kottantharayil A (2011) Enhanced electrostatic integrity of short-channel junctionless transistor with high-k spacers. IEEE Electron Device Lett 32(10):1325–1327

Amin SI, Sarin RK,2016. Enhanced analog performance of doping-less dual material and gate stacked architecture of junctionless transistor with high -k spacer. Appl Phys A 122(4):380

Sahay S, Kumar MJ (2017) Diameter dependence of leakage current in nanowire junctionless field effect transistors. IEEE Trans Electron Devices 64(3):1330–1335. https://doi.org/10.1109/TED.2016.2645640

Devi L, Beloni K, Singh J, Kumar, Srivastava A (2019)Triple-sided charged plasma symmetric lateral bipolar transistor on SiGe-OI. Semicond Sci Technol 34(5):055019

Gnani E, Reggiani S, Rudan M et al (2006) Design considerations and comparative investigation of ultra-thin SOI, double-gate and cylindrical nanowire FETs. In: Proc ESSDERC, pp 371–374

Singh A, Chaudhury S, Pandey CK, Sharma SM, Sarkar CK (2019) Design and analysis of high k silicon nanotube tunnel FET device. IET Circuits Devices Syst 13(8):1305–1310

Fahad HM, Smith CE, Rojas JP, Hussain MM (2011) Silicon nanotube field effect transistor with core–shell gate stacks for enhanced high-performance operation and area scaling benefits. Nano Lett 11(10):43934399

Kumar R, Kumar A (2021)Hetro-Dielectric(HD)Oxide-Engineered Junctionless Double Gate all around (DGAA) Nanotube Field Effect Transistor (FET). Silicon 13:2177–2184

Acknowledgements

The Authors are thankful to lab member Dr. Beloni, Dr. Kundan, and Chakresh Jain for their technical discussion. One of the Authors would like to thank JNU and UGC NFSC for their continuous scholarship support. The authors are also thankful to Ashutosh Bhardwaj, Professor, Department of Physics and Astrophysics, University of Delhi, for providing access to Silvaco TCAD tool for carring out simulation study of this research work.

Author information

Authors and Affiliations

Contributions

All authors contributed to the design and simulation. Material preparation, data collection, and analysis were performed by Rakesh Kumar. The first draft of the manuscript was written by Rakesh Kumar and all authors commented in previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate:

Not Applicable.

Consent for Publication

Not Applicable.

Conflicts of Interest/Competing Interests

The authors have declared that no competing interests exist.

Disclosure of Potential Conflicts of Interest

No conflicts to report.

Research involving Human Participants and/or Animals

Not applicable.

Informed Consent

Not applicable.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, R., Kumar, J. Novel Linearly Graded Nanotube Field-Effect Transistors for Improved Analog Performance and Reduced Leakage Current. Silicon 14, 6271–6278 (2022). https://doi.org/10.1007/s12633-021-01400-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01400-0