Abstract

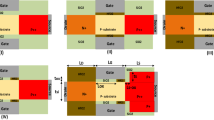

In this paper, the use of hetero-dielectric in quadruple gate Tunnel Field Effect Transistor (QG-TFET) is proposed to simultaneously improve the ON current and the ON-OFF ratio. The analytical models for the surface potential and the electric field for the QG-TFET are obtained by solving 2D-Poisson equations with appropriate boundary conditions. The analytical solution for band-to-band generation is obtained using Kane’s formula and used to calculate the drain current. It is observed that the proposed device structure provides better performance in terms both higher ON current as 10− 3 A/µm and reduced OFF current as 10− 12 A/µm. The obtained ON-OFF ratio with the proposed device structure is 109. The performance of the proposed structure is confirmed by the comparison of the results of analytics with the simulation results obtained using TCAD. The excellent correlation of the modelled results with the simulation results validates the proposed models’ accuracy.

Similar content being viewed by others

Code Availability

Not Applicable.

References

Choi WY, Park B-G, Lee JD, Liu T-JK(2007) Tunneling Field-Effect Transistors (TFETs) with Subthreshold Swing (SS) less than 60 mV/dec. https://doi.org/10.1109/LED.2007.901273

Wang P-F, Hilsenbeck K, Nirschl T, Oswald M, Stepper C, Weiss M, Schmitt-Landsiedel D, Hansch W (2004) Complementary tunneling transistor for low power applications. Solid State Electron. https://doi.org/10.1016/j.sse.2004.04.006

Nirschl T, Weis M, Fulde M, Schmitt-Landsiedel D (2007) Correction to revision of tunneling field-effect transistor in standard CMOS technologies. IEEE Electron Device Lett. https://doi.org/10.1109/LED.2007.893272

Seabaugh AC, Zhang Q (2010)Low-voltage tunnel transistors for beyond CMOS logic, Proc. IEEE. https://doi.org/10.1109/JPROC.2010.2070470

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy efficient electronic switches. Nature. https://doi.org/10.1038/nature10679

Virani HG, Adari RBR, Kottantharayil A (2010)Dual-k spacer device architecture for the improvement of performance of silicon n-channel tunnel FETs. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2010.2057195

Sant S, Schenk A (2016) Methods to enhance the performance of InGaAs/InP heterojunction tunnel FETs. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2015.2489844

Walke AM (2014) Fabrication and analysis of a Si/Si0.55Ge0.45 heterojunction line tunnel FET. IEEE Trans Electron Devices. https://doi.org/10.1109/ted.2014.2299337

Zhou G et al (2012)InGaAs/InP tunnel FETs with a subthreshold swing of 93 mV/dec and ION/IOFF ratio near 106. IEEE Electron Device Lett. https://doi.org/10.1109/led.2012.2189546

Hanna AN, Hussain MM (2015)Si/Gehetero-structure nanotube tunnel field effect transistor. J Appl Phys. https://doi.org/10.1063/1.4905423

Rooyackers R et al (2013) A new complementary hetero-junction vertical tunnel-FET integration scheme. In: IEDM Tech Dig. https://doi.org/10.1109/IEDM.2013.6724558

Cui N, Liang R, Wang J, Xu J,(2012) Two-dimensional analytical model of hetero strained Ge/strained Si TFET, in Proc. Int. Silicon- Germanium Technol. Device Meeting (ISTDM). https://doi.org/10.1109/ISTDM.2012.6222412

Chander S, Baishya S,(2016) Two-dimensional model of a heterojunction silicon-on-insulator tunnel field effect transistor. Superlattice Microst. https://doi.org/10.1016/j.spmi.2015.12.013

Mehta JU, Borders WA, Liu H, Pandey R, Datta S, Lunardi L (2016)III–V tunnel FET model with closed-form analytical solution. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2015.2471808

Wu J, Taur Y (2016) A continuous semianalytic current model for DG and NW TFETs. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2015.2509468

Yunpeng Dong L, Zhang X, Lin M, Chan (2016) A compact model for double gate heterojunction tunnel FTEs. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2016.2604001

Danial Keighobadi S, Mohammadi M, Fathipour (2019) An analytical drain current model for the cylindrical channel gate all around heterojunction tunnel FETs. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2019.2922232

Yunhe Guan Z, Li W, Zhang Y, Zhang, Feng Liang (2018) An analytical model of gate-all-around heterojunction tunneling FET. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2017.2783911

Venkatesh M, Suguna M, Balamurugan NB (2019) Subthreshold performance analysis of germanium source dual halo dual dielectric triple material surrounding gate tunnel field effect transistor for ultra low power applications. J Electron Mater. https://doi.org/10.1007/s11664-019-07492-0

Kane EO (1960) Zener tunneling in semiconductors. J Phys ChemSolids. https://doi.org/10.1016/0022-3697(60)90035-4

Kumar S, Singh K, Chander S, Goel E, Singh PK, Baral K, Singh B, Jit S (2018)2-D analytical drain current model of double-gate heterojunction TFETs with a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2017.2773560

Acknowledgements

We thank VIT University, Vellore for supporting this research work to carry out simulation using TCAD Simulator.

Author information

Authors and Affiliations

Contributions

Conceptualization, Methodology and original draft preparation: [M.Sathishkumar], Supervision [T.S.Arun Samuel], Formal Analysis and Investigation [P.Vimala], Checked the comparison results and validation: [D.Nirmal]

Corresponding author

Ethics declarations

Conflicts of Interest/Competing Interests

The authors have no conflicts of interest to declare that are relevant to the content of this article.

Ethics Approval and Consent to Participate

All authors freely agreed and gave their consent for the publication of this paper.

Consent for Publication

All authors freely agreed and gave their consent for the publication of this paper.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sathishkumar, M., Samuel, T.S.A., Vimala, P. et al. Performance Analysis of HfO2-SiO2 Stacked Oxide Quadruple Gate Tunnel Field Effect Transistor for Improved ON Current. Silicon 14, 6003–6008 (2022). https://doi.org/10.1007/s12633-021-01394-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01394-9