Abstract

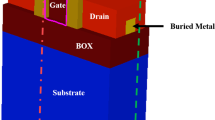

In this work, we propose a Germanium Fin Buried Oxide (FinBOX) Fin Electron-Hole Bilayer Tunnel FET (FBF-EHBTFET) structure. The proposed structure eliminates the gated underlaps and corner effect and also leads to an improved parasitic performance. This also reduces the device base area by ~ 25%. Further, the FinBOX provides an improved OFF state leakage suppression of more than three orders in comparison to the conventional FinEHBTFET. The proposed FinBOX EHBTFET with vertical non-gated underlaps also provides an excellent ION/IOFF ratio > 2 × 108 at VGS=VDS = 0.5 V. Furthermore, the leakage suppression and reduced miller capacitance effect provides an excellent transient response with a better voltage scalability window when scaled from VDD = 0.5 V to 0.4 V. A ~ 41% improved total propagation delay is achieved at VDD = 0.4 V with ~ 61% suppressed overshoot.

Similar content being viewed by others

References

Taur Y (2002) CMOS design near the limit of scaling. IBM J Res Dev 46(2.3):213–222

Sun S-W, Tsui PGY (1995) Limitation of CMOS supply-voltage scaling by MOSFET threshold-voltage variation. IEEE J Solid-State Circ 30(8):947–949

Wang J, Lundstrom M (2002) Does source-to-drain tunneling limit the ultimate scaling of MOSFETs?, Digest. International Electron Devices Meeting,, San Francisco, 707–710

Frank DJ, Dennard RH, Nowak E, Solomon PM, Taur Y, Wong H-SP (2001) Device scaling limits of Si MOSFETs and their application dependencies. Proc IEEE 89(3):259–288

Zhai B, Blaauw D, Sylvester D, Falutner K (2004) Theoretical and Practical Limits of Dynamic Voltage Scaling, in Proceedings of the 41st annual Design Automation Conference, San Diego, CA, USA, 868–873

Frank DJ (2002) Power-constrained CMOS scaling limits. IBM J Res Dev 46(2.3):235–244

Boucart K, Ionescu AM (2007) Length scaling of the Double Gate Tunnel FET with a high-k gate dielectric. Solid-State Electron 51(11):1500–1507

Bhuwalka KK, Born M, Schindler M, Schmidt M, Eisele TSI (2006) P-channel Tunnel Field-Effect Transistors down to Sub-50nm Channel Lengths. Japanese J Appl Phys 45(4B):3106–3109

Wu J, Min J, Taur Y (2015) Short-Channel effects in tunnel FETs. IEEE Trans Electron Dev 62(9):3019–3024

Singh A, Kumar N, Amin SI, Anand S (2020) Implementation of negative capacitance over SiGe sourced doping-less tunnel FET. Superlattice Microst 145:106580. https://doi.org/10.1016/j.spmi.2020.106580

Sarkar D, Xie X, Liu W, Cao W, Kang J, Gong Y, Kraemer S, Ajayan PM, Banerjee K (2015) A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526(7571):91–95

Madan J, Dassi M, Pandey R, Chaujar R, Sharma R (2020) Numerical analysis of Mg2Si/Si heterojunction DG-TFET for low power/high performance applications: impact of nonidealities. Superlattice Microst 139:106397. https://doi.org/10.1016/j.spmi.2020.106397

Der Agopian PG, Martino JA, Vandooren A (2017) Study of line-TFET analog performance comparing with other TFET and MOSFET architectures. Solid State Electron 128:43–47

Zhou G, Li R, Vasen T, Qi M, Chae S, Lu Y et al. (2012) Novel gate-recessed vertical InAs/GaSb TFETs with record high ION of 180 μA/μm at VDS = 0.5 V, in Proc. IEEE IEDM, 32.6.1–36.6.4

Ashita S, Loan A, Rafat M (2018) A high-performance inverted-C tunnel junction FET with Source–Channel overlap pockets. IEEE Trans Electron Dev 65(2):763–768

Lattanzio L, Michielis LD, Ionescu AM (2012) The Electron-hole bilayer tunnel FET. Solid State Electron 74:85–90

Lattanzio L, De Michielis L, Ionescu AM (2012) Complementary germanium Electron–hole bilayer tunnel FET for Sub-0.5-V operation. in IEEE Electron Dev Lett 33(2):167–169

Ashita A, Loan SA, Rafat M (2019) p-Heterogate Ge EHBTFET with asymmetric dielectric underlap pockets, 2019 IEEE 14th Nanotechnology Materials and Devices Conference (NMDC), Stockholm, Sweden, 1–4, doi: https://doi.org/10.1109/NMDC47361.2019.9083986

Ashita S, Loan A, Alharbi AG, Rafat M (2018) Ambipolar leakage suppression in electron-hole bilayer TFET: investigation and analysis, in J Comput Electron. https://doi.org/10.1007/s10825-018-1184-y

Zhu Z, Zhu H, Xu M, Zhong J, Zhao C, Chen D, Ye T (2014) A novel fin Electron–hole bilayer tunnel field-effect transistor. IEEE Transactions on Nanotechnology 13(6):1133–1137

Kim S, Choi WY, Park B (2018) Vertical-structured Electron-hole bilayer tunnel field-effect transistor for extremely low-power operation with high scalability. IEEE Trans Electron Dev 65(5):2010–2015. https://doi.org/10.1109/TED.2018.2817569

Padilla JL, Alper C, Gamiz F, Ionescu AM (2016) Assessment of confinement-induced band-to-band tunneling leakage in the FinEHBTFET, 2016 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Vienna, 20–23

Sentaurus User Guide, J-2014.09

Wu W, Chan M (2007) Analysis of geometry-dependent parasitics in multifin doublegate FinFETs. IEEE Trans Electron Dev 54(4):692–698

Jovanovi V, Suligoj T, Poljak M, Civale Y, Nanver LK (2010) Ultra-high aspect-ratio FinFET technology. Solid State Electron 54(9):870–876

Jain P, Rastogi P, Yadav C, Agarwal A, Chauhan YS (2017) Band-to-band tunneling in \$\Gamma \$ valley for Ge source lateral tunnel field effect transistor: Thickness scaling, in J. Appl. Phys., vol. 122, no. 1, p. 014502, doi: https://doi.org/10.1063/1.4991482

Ashita S, Loan A, Rafat M (2017) A novel finbox EHBTFET for low power applications, 2017 International conference on Microelectronic Devices, Circuits and Systems (ICMDCS), Vellore, pp. 1-4

Padilla JL, Alper C, Godoy A, Gámiz F, Ionescu AM (2015) Impact of asymmetric configurations on the Heterogate germanium Electron–hole bilayer tunnel FET including quantum confinement. IEEE Trans Electron Dev 62(11):3560–3566

Mameli A, Merkx MJM, Karasulu B, Roozeboom F, Kessels WMM, Mackus AJM (2017) Area-Selective Atomic Layer Deposition of SiO2 Using Acetylacetone as a Chemoselective Inhibitor in an ABC-Type Cycle. ACS Nano 11(9):9303–9311

Posseme N, Pollet O, Barnola S (2014) Alternative process for thin layer etching: application to nitride spacer etching stopping to silicon germanium. Appl Phy Lett 105:051605

Jamison PC, Tsunoda T, Vo TA, Li J, Jagannathan H, Shinde SR, Paruchuri VK, Gall D (Sept. 2015) SiO2Free HfO2Gate dielectrics by physical vapor deposition. IEEE Trans Electron Dev 62(9):2878–2882

Stevens E, Tomczak Y, Chan BT, Sanchez EA, Parsons GN, Delabie A (2018) Area-Selective Atomic Layer Deposition of TiN, TiO2, and HfO2 on Silicon Nitride with inhibition on Amorphous Carbon. Chem Mater 30(10):3223–3232

Eminente S, Cristoloveanu S, Clerc R, Ohata A, Ghibaudo G (2007) Ultra-thin fully-depleted SOI MOSFETs: special charge properties and coupling effects. Solid State Electron 51:239–244

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009) On enhanced miller capacitance effect in Interband tunnel transistors. IEEE Electron Dev Lett 30(10):1102–1104

Acknowledgments

This work was supported by the Council of Scientific and Industrial Research (CSIR), Government of India through Senior Research Fellowship scheme (File No. 09/466 (0213)/ 2 K19-EMR-II). The authors would also like to acknowledge the support from Taif University Researchers Supporting Project number (TURSP-2020/264), Taif University, Saudi Arabia.

Availability of Data and Material

NA

Funding

NIL

Author information

Authors and Affiliations

Contributions

All authors contribute in this research work, however, Ms Ashita's contribution in Design, Simulation, Analysis etc. in Substantial.

Corresponding author

Ethics declarations

Ethical standards maintained.

Consent to Participate

YES

Consent for Publication

YES

Conflict of Interest

NIL

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ashita, Loan, S.A., Alkhammash, H.I. et al. A FinBOX Based Ge FinEHBTFET: Design and Investigation. Silicon 14, 2165–2174 (2022). https://doi.org/10.1007/s12633-021-01006-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01006-6