Abstract

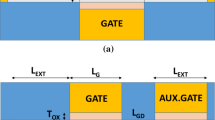

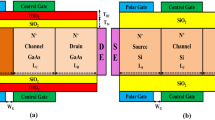

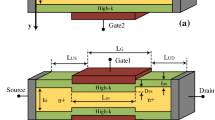

With inherent structural simplicity due to the omission of ultrasteep p-n junctions, the conventional junctionless FET can be used as a barrier-controlled device with low OFF-current in the nanoscale regime. In this work, numerous performance parameters of conventional double-gate junctionless FET namely threshold voltage, OFF-current, ON-current, ON-to-OFF current ratio, and subthreshold slope have been investigated for the range of gate work function from 4.6 eV to 5.6 eV. The performance of conventional double-gate junctionless FET has been further improved with the proposed recessed double-gate junctionless FET using recessed silicon film in the channel region and it has been found that for the gate work function of 5.1 eV (mid-value) the proposed device shows OFF-current of the order of ~ 10− 14 A/µm, ON-to-OFF current ratio of the order of 1010 and subthreshold slope of 65.6 mV/dec as compared to the conventional double-gate junctionless FET. Interestingly, a range of work function values have been found to obtain the optimum performance from the conventional and proposed recessed double-gate junctionless FETs for low power applications. In the work function window, the variations in transconductance and gate-to-source capacitance for both junctionless devices have been illustrated. The impact of different values of the work function of the two gate electrodes for both junctionless devices has also been presented and it is found that the proposed device reflects robustness with nearly constant subthreshold slope.

Similar content being viewed by others

References

A bright future for Moore’s law (2020) https://veturebeat.com/2020/01/07/a-bright-future-for-moores-law/. Accessed 07 Jan 2020

Colinge JP, Lee CW, Afzalian A, Akhvan ND, Yan R, Ferain I, Razavi P, O’Neil B, Blake A, White M, Kelleher AM (2010) Nanowire transistors without junctions. Nat Nanotechnol 5(3):225–229

Jazaeri F, Sallese JM (2018) Modeling nanowire and double-gate junctionless field-effect transistors. Cambridge University Press, Cambridge

Lee CW, Ferain I, Afzalian A, Yan R, Akhavan ND, Razavi P, Colinge JP (2010) Performance estimation of junctionless multigate transistors. Solid State Electron 54:97–103

Lee CW, Nazarov AN, Ferain I, Akhavan ND, Yan R, Razavi P, Yu R, Doria RT, Colinge JP (2010) Low subthreshold slope in junctionless multigate transistors. Appl Phys Lett 96(10):102106

Lee CW, Borne A, Ferain I, Afzalian A, Akhavan ND, Razavi P, Colinge JP (2010) High-temperature performance of silicon junctionless MOSFETs. IEEE Trans Electron Devices 57(3):620–625

Colinge JP, Lee CW, Ferain I, Akhavan ND, Yan R, Razavi P, Yu R, Nazarov AN, Doria RT (2010) Reduced electric field in junctionless transistors. Appl Phys Lett 96(7):073510

Nazarov A (2011) Semiconductor-on-insulator materials for nanoelecronics applications, engineering materials. Springer-Verlag, Berlin, Heidelberg

Cho M, Lee JD, Aoulaiche M, Kaczer B, Roussel P, Kauerauf T, Degraeve R, Franco J, Ragnarsson LA, Groeseneken G (2012) Insight into N/PBTI mechanisms in sub-1-nm-EOT devices. IEEE Trans Electron Devices 59(8):2042–2048

Grasser T (2014) Bias temperature instability for devices and circuits. Springer Science, New York

Toledano-Luque M, Matagne P, Sibaja-Hern´andez A, Chiarella T, Ragnarsson LA, Sor´ee B, Cho M, Mocuta A, Thean A (2014) Superior reliability of junctionless pFinFETs by reduced oxide electric field. IEEE Electron Device Lett 35(12):1179–1181

Singh P, Singh N, Miao J, Park WT, Kwong DL (2011) Gate-all-around junctionless nanowire MOSFET with improved low-frequency noise behaviour. IEEE Electron Device Lett 32(12):1752–1754

Lee CW, Afzalian A, Akhvan ND, Yan R, Ferain I, Colinge JP (2009) Junctionless multigate field-effect-transistors. Appl Phy Lett 94(9):053511–053512

Deleonibus S (2019) Emerging devices for low-power and high-performance nanosystems: physics, novel functions and data processing. Temasek Bouleward Singapore

Park JT, Kim JY, Colinge JP (2012) Negative-bias-temperature-instability and hot carrier effects in nanowire junctionless p-channel multigate transistors. Appl Phys Lett 100(8):083504

Gnudi A, Reggiani S, Gnani E, Baccarani G (2012) Analysis of threshold voltage variability due to random dopant fluctuations in junctionless FETs. IEEE Electron Device Lett 33(3):336–338

Nawaz SM, Mallik A (2016) Effects of device scaling on the performance of junctionless FinFETs due to gate-metal work function variability and random dopant fluctuations. IEEE Electron Device Lett 37(8):958–961

Giusi G, Lucibello A (2014) Variability of the drain current in junctionless nanotransistors induced by random dopant fluctuation. IEEE Trans Electron Devices 61(3):702–706

Sahay S, Kumar MJ (2016) Controlling L-BTBT and volume depletion in nanowire JLFETs using core-shell architecture. IEEE Trans Electron Devices 63(9):3790–3794

Lee SM, Jang HJ, Park JT (2013) Impact of back gate biases on hot carrier effects in multiple gate junctionless transistors. Microelectron Reliab 53(9):1329–1332

Jacob AP, Xie R, Sung MG, Liebmann L, Lee RTP, Taylor B (2017) Scaling challenges for advanced CMOS devices. Int J High Speed Electron Syst 26(1):17400011–174000176

Taur Y, Chen HP, Wang W, Lo SH, Wann C (2012) ON-off charge-voltage characteristics and dopant number fluctuation effects in junctionless double-gate MOSFETs. IEEE Electron Device Lett 59(3):863–866

Sallese JM, Jazeri F, Barbut L, Chevillon N, Lallement C (2013) A common core model for junctionless nanowires and symmetric double-gate FETs. IEEE Trans Electron Devices 60:4277–4280

Jiang C, Liang R, Wang J, Xu J (2015) A two-dimensional analytical model for short channel junctionless double-gate MOSFETs. AIP Adv 5(5):057122

Jazeri F, Barbut L, Sallese JM (2014) Modeling asymmetric operation in double-gate junctionless FETs by means of symmetric devices. IEEE Trans Electron Devices 61(12):3962–3972

Oproglidis TA, Tsormpatzoglou A, Tassis DH, Karatsori TA, Barraud S, Ghibaudo G, Dimitriadis CA (2017) Analytical drain current compact model in the depletion operation region of short-channel triple-gate junctionless transistors. IEEE Trans Electron Devices 64(1):66–72

Trevisoli R, Doria RT, Souza MD, Barraud S, Vinet M, Pavanello MA (2016) Analytical model for the dynamic behavior of triple-gate junctionless nanowire transistors. IEEE Trans Electron Devices 63(2):856–863

Han MH, Chang CY, Jhan YR, Wu JJ, Chen HB, Cheng YC, Wu YC (2013) Characteristic of p-type junctionless gate-all-around nanowire transistor and sensitivity analysis. IEEE Electron Device Lett 34(2):157–159

Djeffal F, Ferhati H, Bentrcia T (2016) Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattice Microstruct 90:132–140

Baruah RK, Paily RP (2013) Impact of high-k spacer on device performance of a junctionless transistor. J Comput Electron 12:14–19

Kumar MPV, Hu CY, Kao KH, Lee YJ, Chao TS (2015) Impacts of the shell doping profile on the electrical characteristics of junctionless FETs. IEEE Trans Electron Devices 62(11):3541–3546

Singh B, Gola D, Goel E, Kumar S, Singh K, Jit S (2016) Dielectric pocket double-gate junctionless FET: A new MOS structure with improved subthreshold characteristics for low power VLSI applications. J Comput Electron 15:502–507

Jaiswal N, Kranti A (2018) Modeling short-channel effects in asymmetric junctionless MOSFETs with underlap. IEEE Trans Electron Devices 65(9):3669–3675

Lee L, Ku CS, Ke WC, Ho CW, Huang HY, Lee MC, Chen WH, Chou WC, Chen WH (2006) Current properties of GaN V-defect using conductive atomic force microscopy. Jpn J Appl Phys 45(31):L817–L820

Jaiswal N, Kranti A (2019) Modeling short-channel effects in core-shell junctionless MOSFET. IEEE Trans Electron Devices 66(1):292–299

Hirpara Y, Saha R (2020) Analysis on DC and RF/Analog performance in Multifin-FinFET for wide variation in work function of metal gate. Silicon. https://doi.org/10.1007/s12633-020-00408-2

Parihar MS, Kranti A (2014) Revisiting the doping requirement for low power junctionless MOSFETs. Semicond Sci Technol 29:075006–075016

Soree B, Magnus W, Vandenberghe W (2011) Low-field mobility in ultrathin silicon nanowire junctionless transistors. Appl Phys Lett 99:235091–235093

Sahay S, Kumar MJ (2019) Junctionless field-effect-transistor: design, modeling, and simulation. Jon Wiley & Sons Inc, Hoboken, New Jersey

Robertson J (2004) High dielectric constant oxides. Eur Phys J Appl Phys 28:265–291

Wilk GD, Wallace RM, Anthony JM (2001) High-k gate dielectrics: Current status and material properties considerations. J Appl Phys 89(10):5243–5275

Robertson J (2005) Interfaces and defects of high-k oxides on silicon. Solid State Electron 49:283–293

Jacobson DL, Campbell AE (1971) Molybdenum work function determined by electron emission. Microsc Metall Trans 2:3063–3066

Atlas User’s Manual (2016), Silvaco, Santa Clara

Allen PE, Holberg DR (2002) CMOS analog circuit design, Oxford University Press, Oxford

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Conflict of interest/Competing interests

Not Applicable.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, S., Chatterjee, A.K. & Pandey, R. Performance Analysis of Gate Electrode Work Function Variations in Double-gate Junctionless FET. Silicon 13, 3447–3459 (2021). https://doi.org/10.1007/s12633-020-00774-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00774-x