Abstract

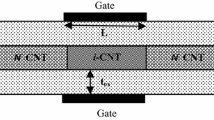

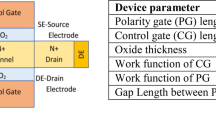

In this work, we developed and explored the CMOS circuits ring oscillator with n- and p-channel on scaled SB-FETs for low power applications. Newly, a source-side charge plasma schottky barrier (SB) SB-FETs have been acquainted as the furthermost practical at nano-meter node technology. So, it is essential to examine the electrical characteristics of SB-FETs and their performance. Initially, we have been explored the source-side charge plasma SB-FET and its electrical characteristics has been simulated in compared with conventional SB-FET. The SILVACO simulator is used to simulate the proposed and conventional SB-FETs. In this source-side charge plasma SB-FET technique has improved resolution, and deliver outstanding concert (higher Ion/Ioff ratio) than conventional device reported in this research. Moreover, the precise exploration of the on-state performance of SB-FETs is mostly resolved by the electron and hole energy band of the channel. Additional, for the first time, source-side charge plasma SB-FET-based CMOS inverter and ring oscillator circuits have been calculated by the numerical simulator. The concentrated gate capacitance also grades in compact dynamic power degeneracy of source-side charge plasma schottky barrier SB-FET CMOS circuits and ring oscillator suggest lower voltage of process with condensed power intake, and great noise protection compared with convention device.

Similar content being viewed by others

References

Song JY, Choi WY, Park JH, Lee JD, Park B-G (2006) Design optimization of gate-all-around (GAA) MOSFETs. IEEE Trans Nanotechnology 5:186–191. https://doi.org/10.1109/TNANO.2006.869952

Bhuwalka KK, Schulze J, Eisele I (2005) Scaling the vertical tunnel FET with tunnel Bandgap modulation and gate Workfunction engineering. IEEE Trans Electron Devices 52:909–917. https://doi.org/10.1109/TED.2005.846318

Yang W, Yu Z, Tian L (2007) Scaling theory for FinFETs based on 3-D effects investigation. IEEE Trans Electron Devices 54:1140–1147. https://doi.org/10.1109/TED.2007.893808

Kumar P, Bhowmick B (2017) 2D analytical model for surface potential based electric field and impact of wok function in DMG SB MOSFET. Superlattice Microst 109:805–814. https://doi.org/10.1016/j.spmi.2017.06.001

Kumar P, WasimArif BB (2018) Scaling of dopant segregation Schottky barrier using metal strip buried oxide MOSFET and its comparison with conventional device. Silicon 10:811–820. https://doi.org/10.1007/s12633-016-9534-5

Kumar P, Bhowmick B (2018) Comparative analysis of hetero gate dielectric hetero structure tunnel FET and Schottky barrier FET with n+ pocket doping for suppression of Ambipolar conduction and improved RF/linearity. J Nanoelectron Optoelectron. https://doi.org/10.1166/jno.2018.2488

Kumar P, Bhowmick B (2018) Suppression of ambipolar conduction and investigation of RF performance characteristics of gate-drain underlap SiGe Schottky barrier field-effect transistor. Micro & Nano Letters 13:626–630. https://doi.org/10.1049/mnl.2017.0895

Kumar P, Bhowmick B A physics-based threshold voltage model for hetero-dielectric dual material gate Schottky barrier MOSFET. Int J Numer Model https://doi.org/10.1002/jnm.2320

International Technology Roadmap for Semiconductors. San Jose: Semiconductor Association, 2013

Trivedi VP, Fossum JG (2005) Quantum-mechanical effects on the threshold voltage of undoped double-gate MOSFETs. IEEE Electron Device Lett 26:579–582. https://doi.org/10.1109/LED.2005.852741

ATLAS (2015) Device simulation software. Silvaco Int, Santa Clara

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Devices 57:2317–2319. https://doi.org/10.1109/TED.2010.2052167

Rhoderick EH (1982) Metal-semiconductor contacts. IEE Proceedings I - Solid-State and Electron Devices 1:1. https://doi.org/10.1049/ip-i-1.1982.0001

P Kumar B. Bhowmick, A Vinod “Impact of Ferroelectric on the Electrical Characteristics of Silicon–Germanium based heterojunction Schottky Barrier MOSFET”, https://doi.org/10.1016/j.aeue.2019.05.030

Kumar P, Bhowmick B (2017) 2-D analytical modeling for electrostatic potential and a threshold voltage of a dual work function gate Schottky barrier MOSFET. J Comput Electron 16:658–665. https://doi.org/10.1007/s10825-017-1011-x

Lombardi C, Manzini S, Saporito A, Vanzi M (1988) A physically-based mobility model for numerical simulation of nonplanar devices. IEEE Trans Comput-Aided Des Integr Circuits Syst 7:1164–1171. https://doi.org/10.1109/43.9186

Kumar P, Bhowmick B (2019) Source-drain junction engineering Schottky barrier MOSFETs and their mixed mode application. Silicon. 12:1–10. https://doi.org/10.1007/s12633-019-00170-0

Hui-Wen Cheng, Hwang C-H, Li Y (2009) Propagation delay dependence on channel fins and geometry aspect ratio of 16-nm multi-gate MOSFET inverter. 2009 1st Asia Symposium on Quality Electronic Design, Kuala Lumpur, Malaysia: IEEE; p. 122–5. https://doi.org/10.1109/ASQED.2009.5206287

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

R, K.K., S, S. Design and Performance of Charge-Plasma-Based Schottky –FET CMOS Circuit Ring Oscillator for High Density ICs. Silicon 13, 2581–2587 (2021). https://doi.org/10.1007/s12633-020-00581-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00581-4