Abstract

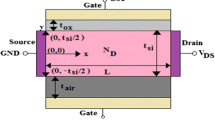

In this article, the electrical behavior of short channel SiGe Heterostructure Junction-Less DG-MOSFET have been studied by incorporating the quantum mechanical effect and short channel effects. Analytical model and simulation result shows how the device process parameters like gate oxide thickness, silicon thickness, channel doping concentration, channel or gate length etc. have an impact on the D.C parameters like threshold voltage, surface potential. DIBL and threshold voltage of the nanoscale JL-MOSFET are also analyzed by considering the QME to raise the accuracy of the derived models. Extensive simulations are performed in SILVACO ATLAS TCAD tool to validate the proposed models. It is quite evident that the derived models and simulation results are in good agreement for a wide variation of process parameters. Schrodinger model has been used in ATLAS simulation platform to validate the derived analytical model considering QME. However, comprehensive analysis of the short channel SiGe Hetero-structure Junction-Less Double Gate Metal Oxide Semiconductor Field Effect Transistor gives a better view and understanding of D.C characteristics of the device. At the end, D.C characteristics (power dissipation, propagation delay, power-delay product) of an inverter circuit has been taken under consideration to check the impact of QMEs on circuit performance.

Similar content being viewed by others

References

Kundu S, Mohanty SP, Ranganathan N (2013) Design methodologies for nano-electronic digital and analogue circuits. IET Circuits Devices Syst 7(5):221–222

Lee, C.-W., Nazarov, A.N., Ferain, I., Akhavan, N.D., Yan, R., Razavi, P., Yu, R., Doria, R.T., Colinge, J.-P. et al. Low subthreshold slope in junctionless multigate transistors. Appl.Phys.Lett.96(10), 102106–1–102106-3 (2010)

Jazaeri F, Barbut L, Koukab A, Sallese J-M et al (Apr.2013) Analytical model for ultra-thin body junctionless symmetric double gate MOSFETs in subthreshold regime. Solid State Electron 82:103–110

Dehzangi A, Larki F, Hutagalung SD, Saion EB, Abdullah AM, Hamidon MN, Majlis BY, Kakooei S, Navaseri M, Kharazmi A et al (2012) Numerical investigation and comparison with experimental characterisation of side gate p-type junctionless silicon transistor in pinch-off state. IET Micro and Nano Letters 7(9):981–985

Vadizadeh, Mahdi. et al. “Designing a Hetrostructure Junctionless-Field Effect Transistor (HJL-FET) for High-Speed Applications.” Journal of the Korean Physical Society 71, no. 5 (2017): 275–82. https://doi.org/10.3938/jkps.71.275

Colinge J-P, Alderman JC, Xiong W, Cleavelin CR et al (May 2006) Quantum–mechanical effects in trigate SOI MOSFETs. IEEE Trans Electron Devices 53(5):1131–1136

Gupta S, Ghosh B, Rahi SB et al (2015) Compact analytical model of double gate junction-less field effect transistor comprising quantum-mechanical effect. J Semicond 36(2):024001. https://doi.org/10.1088/1674-4926/36/2/024001

Jazaeri F, Barbut L, Sallese JM (2013) Modeling and design space of junctionless symmetric DG MOSFETs with long channel. IEEE TED 60(7):2120–2127

Sallese, J.M., Chevillon, N.,Lallement,C.,Iñiguez,B., Prégaldiny, F. et al. Charge-based modeling of junctionless double-gate field-effect transistors. IEEE TED 58(8), 2628–2637 (2011)

SILVACO International 2000, ATLAS: 2-D Device Simulation Software

Pritha Banerjee and Subir Kumar Sarkar et al. "3-D analytical modeling of high-k gate stack dual-material tri-gate strained silicon-on-nothing MOSFET with dual-material bottom gate for suppressing short channel effects", in Journal of Computational Electronics, Springer, Vol.16.No.3,pp-631-6397

Rout SP, Dutta P (2019) Impact of high mobility III-V compound material of a Short Channel thin-film SiGe double gate Junctionless MOSFET as a source. Engineering Reports 2(1). https://doi.org/10.1002/eng2.12086

Arora ND, Hauser JR, Roulston DJ et al (Feb 1982) Electron and hole mobilities in silicon as a function of concentration and temperature. IEEE Trans. Electron Devices 29(2):292–295

Fossum JG, Lee DS et al (1982) A physical model for the dependence of carrier lifetime on doping density in nondegenerate silicon. Solid StateElectron 25:741–747

Saha S et al (Jan. 1995) MOSFET test structures for two-dimensional device simulation. Solid State Electron 38(1):69–73

Chanda M, De S, Sarkar CK et al (2014) Modeling of characteristic parameters for nano-scale junctionless double gate MOSFET considering quantum mechanical effect. J Comput Electron 14(1):262–269

Alioto, Massimo et al. (2010) Closed-form analysis of DC noise immunity in subthreshold CMOS logic circuits. Proceedings of 2010 IEEE International Symposium on Circuits and Systems, https://doi.org/10.1109/iscas.2010.5537340

Sen. D, Sengupta. S. J., Roy. S., Chanda. M., & Sarkar. S. K. et al. “D.C performance analysis of sub-threshold source-coupled logic circuit using double gate junction-less metal oxide semiconductor field effect transistor for low-power application”, Sens Lett, 17(7), 538–545, 2019. doi: https://doi.org/10.1166/sl.2019.4104

Sen, Dipanjan, Savio Jay Sengupta, Swarnil Roy, Manash Chanda, and Subir Kumar Sarkar et al. (2019) Analytical modeling of D.C parameters of double gate junctionless MOSFET in near & subthreshold regime for RF circuit application. Nanoscience &Nanotechnology-Asia 09. https://doi.org/10.2174/2210681209666190730170031

Gao H-W, Wang Y-H, Chiang T-K et al (2018) A new device-parameter-oriented DC power model for symmetric Operation of junction-less double-gate MOSFET working on low-power CMOS subthreshold logic gates. IEEE Trans Nanotechnol 17(3):424–431

Sen D, Banik. B, & Roy S et al. (2018) Power and delay analysis of junction-less double gate cmos inverter in near and sub-threshold regime, IEEE Electron Devices Kolkata Conference (EDKCON). https://doi.org/10.1109/edkcon.2018.8770468

Sengupta SJ, Sen D, Roy S, Chanda M, Sarkar SK et al (2019) D.C. performance analysis of high-K adiabatic logic circuits in sub-threshold regime for RF applications. Sens Lett 17(6):487–496. https://doi.org/10.1166/sl.2019.4102

Acknowledgements

Authors of this paper would like to thank the support obtained from Advanced VLSI Lab, Dept. of ECE, Meghnad Saha Institute of Technology, Kolkata, India.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sen, D., Sengupta, S.J., Roy, S. et al. Analysis of D.C Parameters of Short-Channel Heterostructure Double Gate Junction-Less MOSFET Circuits Considering Quantum Mechanical Effects. Silicon 13, 1165–1175 (2021). https://doi.org/10.1007/s12633-020-00507-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00507-0