Abstract

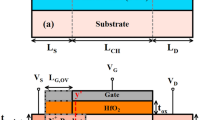

Tunnel FET (TFET) is a significant discovery in the field of low power application, which has the ability to sustain short channel effects arising due to scaling. But the disadvantage of TFET is low ON current, and it is a challenge to maintain a high ON current with very low OFF current, hence it is tough to obtain a higher switching ratio maintaining a low SS. In this paper, to investigate the influence of dimensionality and other electrical parameters on TFET with simulation, a device based on an extended source TFET (ES-TFET) with SiGe pocket layer at the edge of source channel junction is proposed. It shows excellent performance improvement over standard TFET. In this paper, for the first time the effect of increase in length of the extended source has been studied while SS degrades but threshold voltage remains unchanged, also extended source distance from surface degraded effect on SS has been improved with the introduction of SiGe layer. Various scaling parameters have been investigated to study its impact on electrical parameters showing an ON-current of 0.01 mA/μm and OFF-current of 6.48 × 10−17 A/μm neglecting gate leakage for 1 V gate and drain voltage. The Remarkable value of SS of 16 mV/decade and ON-OFF current ratio of more than 1011 for a threshold voltage of 0.4 V is obtained. Scalability of the proposed device according to ITRS is well maintained, and it is validated by its improved performance over the wide range of channel length.

Similar content being viewed by others

References

Chunlei Wu, Qianqian Huang, , Yang Zhao, Jiaxin Wang, Yangyuan Wang and Ru Huang (2016) A novel tunnel FET design with StackedSource configuration for average subthreshold swing reduction. IEEE Trans. on Electron Devices 63(12):5072–5076

Khatami Y, Banerjee K (2009) Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans Electron Devices 56(11):2752–2761

Guo P-F, Yang L-T, Yang Y, Fan L, Han G-Q, Samudra G, Yeo Y-C (2009) Tunneling field-effect transistor: effect of strain and temperature on tunneling current. IEEE Elect Device Lett 30(9):981–983

Jeon K, Loh W-Y, Patel P, Kang Y, Oh J, Bowonder A, Park C, Park C, Smith C, Majhi P, Tseng H-H, Jammy R, Liu T-J, Hu C (2010) Si tunnel transistors with a novel silicided source and 46 mv/dec swing. Proc. VLSIT Symp:121–122

Qin Z, Wei Z, Seabaugh A (2006) Low-subthreshold-swing tunnel transistors. IEEE Electron Device Lett 27(4):297–300

Knoch J, Mantl S, Appenzeller J (2007) Impact of the dimensionality on the performance of tunneling FETs: bulk versus one-dimensional devices. Solid State Electron 51:572–578

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373):329–337

Royer CL, Mayer F (2009) Exhaustive experimental study of tunnel field effect transistors (TFETs):from materials to architecture. Proc. 10th Int. Conf. ULIS, pp, pp 54–56

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans on Electron Devices 54(7):1725–1733

Avci UE, Young IA (2013) Heterojunction TFET scaling and resonant-TFET for steep subthreshold slope at sub-9nm gate-length, 2013 IEEE International Electron Devices Meeting. Washington, DC 4(3):1–4.3.4

Mitra SK, Goswami R, Bhowmick B (2016) A hetero-dielectric stack gate SOI-TFET with back gate and its application as a digital inverter. Superlattice Microst 92:37–41

Wu C, Huang Q, Zhao Y, Wang J, Wang Y, Huangn R (2016) A novel tunnel FET design with stacked source configuration for average subthreshold swing reduction. IEEE Transactions on Electron Devices 63(12):5072–5076

Rupam Goswami and B. Bhowmick (2014) Hetero-gate-dielectric gate-drain underlap nanoscale TFET with a δp+ Si1−xGex layer at source-channel tunnel junction. Proceedings of International Conference on Green Computing Communication and Electrical Engineering (ICGCCEE) Coimbatore pp. 1–5

C. D. Llorente et al. (2018) Innovative tunnel FET architectures. Joint international EUROSOI workshop and international conference on ultimate integration on silicon (EUROSOI-ULIS), Granada pp. 1-4

Christian Philipp Sandow (2011) "Modelling, Fabrication and Characterization of silicon tunnel field effect transistor", PhD Thesis Report, RWTH Aachen, Germany

T.C.A.D. Synopsys, Manual, version. E2010.12

A. A. Chakraborty, P. N. Kondekar, and M. K. Yadav (2012) Drive Current Boosting and Low Sub-threshold Swing Obtained by δp+ Layer in Double-Gate Tunnel FET. ESciNano pp. 1–2

Shih C-H, Chien ND (2014) Design and modeling of line-tunneling field-effect transistors using low-bandgap semiconductors. IEEE Transaction on Electron Devices 61(6):1907–1913

Chien ND, Shih C (2015) Short-channel effect and device design of extremely scaled tunnel field-effect transistors. Microelectron Reliab 55:31–37

Luo Z, Wang H, An N, Zhu Z (2015) A tunnel dielectric-based tunnel FET. IEEE Electron Device Letters 36(9):966–968

Bhushan B, Nayak K, Ramgopal Rao V (2012) DC compact model for SOI tunnel field-effect transistors. IEEE Trans. on Electron Devices 59(10):2635–2642

Dawit Burusie, Mamidala Jagadesh Kumar, (2006), 2-D Threshold Voltage Model for the Double-Gate p-n-p-n TFET with Localized Charges IEEE Transaction on Electron Devices, 63(9)

Mohd Razip Wee, M. F., Dehzangi, A., Bollaert, S., Wichmann, N., & Majlis, B. Y. (2013). Gate length variation effect on performance of gate-first self-aligned In0 .5 3 Ga0 .4 7 As MOSFET. PloS one, 8(12)

Sweta Chander, S. Baishya Impact of channel length and oxide thickness variation in an SGOI-TFET, (2013) IEEE Asia Pacific conference on postgraduate Research in Microelectronics and Electronics (PrimeAsia), 103–106

Orlowski M, Mazure C, Lau F (1987) Submicron short channel effects due to gate reoxidation induced lateral interstitial diffusion. International Electron Devices Meeting, Washington, DC, USA, pp 632–635

Jacobs H, von Schwerin A, Scharfetter D, Lau F (1993) MOSFET reverse short channel effect due to silicon interstitial capture in gate oxide. Proceedings of IEEE International Electron Devices Meeting, Washington, DC, USA, pp 307–310

Boucart K, Ionescu A (2007) Length scaling of the double gate tunnel FET with a high-K gate dielectric. Solid State Electron 51

Nguyen Dang Chien, Chun-Hsing Shih, Hung-Jin Teng, Cong-Kha Pham (2018) Dependence of Short-Channel Effects on Semiconductor Bandgap in Tunnel Field-Effect Transistors, 42nd Vietnam National Conference on Theoretical Physics (NCTP-42),1–6

Hadjisavvas G, Tsetseris L, Pantelides SI (2007) The origin of electron mobility enhancement in strained MOSFETs. IEEE Electron Device Lett 28:1018–1020

Ferhati H, Djeffal F, Bentrcia T (2018) The role of the Ge mole fraction in improving the performance of a nanoscale junctionless tunnelling FET: concept and scaling capability. Beilstein Journal of Nanotechnology 9:1856–1862

Singh TV, Jagadesh Kumar M (2007) Effect of the Ge mole fraction on the formation of a conduction path in cylindrical strained-silicon-on-SiGe MOSFETs. Superlattice Microst 44(2008):79–85

Goswami PP, Bhowmick B (2019) Optimization of electrical parameters of pocket doped SOI TFETwith L shaped gate. Silicon:1–8. https://doi.org/10.1007/s12633-019-00169-7

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Talukdar, J., Rawat, G. & Mummaneni, K. A Novel Extended Source TFET with δp+- SiGe Layer. Silicon 12, 2273–2281 (2020). https://doi.org/10.1007/s12633-019-00321-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00321-3