Abstract

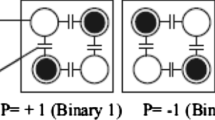

This paper presents the fabrication of single level cell (SLC), multi-level cell (MLC), triple-level cell (TLC) and quadruple level cell (QLC) using quantum dot gate non-volatile memory (QDNVM). QDNVM can store multiple bits in its discrete quantum dots in the gate region which represents different states of the memory cell. The precise control of charge storage in the discrete quantum dots I the gate region of the QDNVM solves the reliability issues of MLC and TLC. Dynamic Random Access Memory (DRAM) is very compact memory device which needs to refresh periodically. Use of QDNVM will increase the bit storing capability of DRAM. Compact design and increase bit handling capability of designed DRAM will help to increase the information density per unit area.

Similar content being viewed by others

References

Hachiya S, Johguchi K, Miyaji K, Takeuchi K (2014) Hybrid triple-level-cell/multi-level-cell NAND flash storage array with chip exchangeable method. Jpn Soc Appl Phys 53(4S):04EE04

Hsiao WY, Mei CY, Shen WC, Chih YD, King Y-C, Lin CJ (2014) A new 28 nm high-k metal gate CMOS logic one-time programmable memory cell. Jpn Soc Appl Phys 53(4S):04ED01

Seong NH, Yeo S, Lee H-HS (2013) Tri-level-cell phase change memory. ACM SIGARCH Comput Arch News 41(3):440–451

Karmakar S, Jain FC (2015) Ternary SRAM using quantum dot gate field effect transistor (QDGFET). IET Micro Nano Lett 10(11):621–624

Karmakar S, Suarez E, Gogna M, Jain F (2012) ZnS-ZnMgS-ZnS lattice-matched gate insulator as an alternative for silicon-dioxide on silicon in quantum dot gate FET (QDGFET). J Electron Mater 41(10):2663–2670. https://doi.org/10.1007/s11664-012-2220-5

Karmakar S, Gogna M, Jain FC (2016) Application of quantum dot gate nonvolatile memory (QDNVM) in image segmentation. In: Signal, image and video processing, pp 1–8

Gogna M, Suarez E, Chan P-Y, Al-Amoody F, Karmakar S, Jain FC (2011) Nonvolatile silicon memory using GeOx – cladded Ge quantum dots self-assembled on SiO2 and lattice-matched II-VI tunnel insulator. J Electron Mater 40(8):769–1774

Karmakar S, Gogna M, Suarez E, Jain FC (2011) Three-state quantum dot gate field-effect transistor in silicon-on-insulator. IET Circuits Devices Syst 9(2):111–18

Karmakar S (2014) Ternary logic gates using quantum dot gate FETs (QDGFETs). Silicon 6(3):169–178

Karmakar S, Gogna M, Suarez E, Alamoody F, Heller E (2009) 3-State behavior of quantum dot gate FETs with lattice matched insulator. In: Nanoelectronic devices for defense and security. Fort Lauderdale

Karmakar S, Jain FC (2015) Circuit model of different quantum dot based field effect transistors. Silicon 7(1):15–26

Karmakar S, Jain FC (2012) Future semiconductor devices for multi-valued logic circuit design. Mater Sci Appl 3(11):807

Karmakar S, Chandy JA, Jain FC (2014) Implementation of six bit ADC and DAC using quantum dot gate non-volatile memory. J Signal Process Syst 75(3):209–216

Karmakar S (2014) Novel three state quantum dot gate FET: fabrication, modeling and application. Springer, Berlin

Jain FC, Suarez E, Gogna M, AlAmoody F, Butkiewicus D, Hohner R, Liaskas T, Karmakar S, Chan PY, Miller B, Chandy J, Heller E (2009) Novel quantum dot gate FETs and nonvolatile memories using lattice-matched II-VI gate insulators. J Electron Mater 38(8):1574–1578

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Karmakar, S. Design of Multi-state DRAM Using Quantum Dot Gate Non-volatile Memory (QDNVM). Silicon 11, 869–877 (2019). https://doi.org/10.1007/s12633-018-9879-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-018-9879-z