Abstract

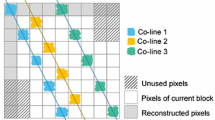

The advanced video compression standard H.264/AVC adopts Rate Distortion Optimization to enhance coding efficiency at the cost of a very high computational complexity. Intra Prediction part is the major processing bottleneck considering total time and power consumption. We therefore propose an efficient parallel processing structure for H.264/AVC 4 × 4 intra prediction. Unlike generic architectures utilizing serial processing with increased time and power consumption, a new processing order is introduced to reduce data dependencies between consecutively executed blocks within H.264/AVC intra prediction. Our experimental results show that the parallel execution of these blocks saves power consumption by up to 22.8% with slight increase in bit rate.

Similar content being viewed by others

References

Jin G H, Lee H J (2006) A parallel and pipelined execution of H.264/AVC intra prediction. The Sixth IEEE International Conference on Computer and Information Technology (CIT’06): 246–251

JVT H.264 (2005) Reference Software Version JM 10.2

Pan F, Lin X, Susanto Rahardja, Keng Pang Lim, Li Z G, Wu D J, Wu S (2005) Fast mode decision algorithm for intra prediction in H.264/AVC video coding. IEEE Trans Circuits and Systems for Video Technology 15(7): 813–822

Kibum Suh, Seongmo Park, Cho H J (2005) An efficient hardware architecture of intra prediction and TQ/IQIT module for H.264 encoder. ETRI Journal 27(5): 511–524

Huang YW, Hsieh B Y, Chen T C, Chen L G (2005) Analysis, fast algorithm, and VLSI architecture design for H.264/AVC intra frame coder. IEEE Trans. Circuit and Systems for Video Technology 15(3): 378–401

Muhammad Shafique, Lars Bauer, Jorg Henkel (2009) A parallel approach for high performance hardware design of intradiction in H.264/AVC video codec. Design, Automation & Test in Europe Conference & Exhibition: 1434–1439

Elleouet D, Julien N, Houzet D, Cousin J G, Martin M (2004) Power consumption characterization and modeling of embedded memories in XILINX. Digital System Design, Euromicro Symposium: 394–401

http://www.xilinx.com/products/design_tools/logic_design/verification/xpower_an.htm

Author information

Authors and Affiliations

Corresponding author

About this article

Cite this article

Ren, Gy., Li, Jj. A novel FPGA-based H.264/AVC intra prediction. Fuzzy Inf. Eng. 3, 183–191 (2011). https://doi.org/10.1007/s12543-011-0076-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12543-011-0076-7