Abstract

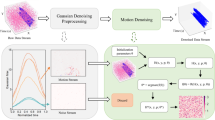

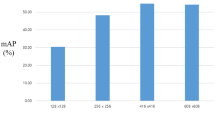

Block-matching and 3D-filtering (BM3D) is a state of the art denoising algorithm for image/video, which takes full advantages of the spatial correlation and the temporal correlation of the video. The algorithm performance comes at the price of more similar blocks finding and filtering which bring high computation and memory access. Area, memory bandwidth and computation are the major bottlenecks to design a feasible architecture because of large frame size and search range. In this paper, we introduce a novel structure to increase data reuse rate and reduce the internal static-random-access-memory (SRAM) memory. Our target is to design a phase alternating line (PAL) or real-time processing chip of BM3D. We propose an application specific integrated circuit (ASIC) architecture of BM3D for a 720×576 BT656 PAL format. The feature of the chip is with 100 MHz system frequency and a 166-MHz 32-bit double data rate (DDR). When noise is σ = 25, we successfully realize real-time denoising and achieve about 10 dB peak signal to noise ratio (PSNR) advance just by one iteration of the BM3D algorithm.

Similar content being viewed by others

References

DABOV K, FOI A, EGIAZARIAN K. Video denoising by sparse 3D transform-domain collaborative filtering [C]//15th European Signal Processing Conference. Poznan Poland: [s. n.], 2007: 7–11.

DABOV K, FOI A, KATKOVNIK V, et al. Image denoising by sparse 3D transform-domain collaborative filtering [J]. IEEE Transactions on Image Processing, 2007, 16(8): 2080–2095.

ZHU S P, HOU Y S, WANGZ K, et al. A novel fractal video coding algorithm using fast block-matching motion estimation technology [C]//International Conference on Computer Application and System Modeling. [s. l.]: IEEE, 2010: 360–364.

YANG H S, LI J, SUN J, et al. Fast block matching algorithm for H. 264/SVC motion estimation based on sub-sampling [C]//International Conference on Computer Engineering and Technology. [s. l.]: IEEE, 2010: 154–157.

JAMIL F H, PORLE R R, CHEKIMA A, et al. Preliminary study of block matching algorithm (BMA) for video coding [C]//4th International Conference on Mechatronics. Kuala Lumpur Malaysia: IEEE, 2011: 1–5.

YAP S Y, MCCANNY J V. A VLSI architecture for variable block size video motion estimation [J]. IEEE Transactions on Circuit and System II, 2004, 51(7): 384–389.

CHEUNG C H, PO L M. A noval small-crossdiamond search algorithm for fast video coding and videoconferencing applications [C]//International Conference on Image Processing. [s. l.]: IEEE, 2002: 681–684.

ZHU S, MA K K. A new diamond search algorithm for fast block-matching motion estimation [J]. IEEE Transactions on Image Processing, 2000, 9(2): 287–290.

ZHU C, LIN X, CHAU L, et al. Enhanced hexagonal search for fast block motion estimation [J]. IEEE Transactions on Circuits and Systems for Video Technology, 2004, 14(10): 1210–1214.

TSAI T H, PAN T N. A novel 3-D predict hexagon search algorithm for fast block motion estimation on H. 264 video coding [J]. IEEE Transactions on Circuits and Systems for Video Technology, 2006, 16(12): 1542–1549.

QIU T F, BADAWY W. The hardware architecture of a novel motion estimator with adaptive crossed quarter polar search patterns for H.264 encoding [C]//Canadian Conference on Electrical and Computer Engineering. [s. l.]: IEEE, 2009: 819–822.

LI B, MA K K. Unequal-arm adaptive rood pattern search with early terminations for fast block-matching motion estimation on H. 264 [C]//IEEE Asia Pacific Conference on Circuits and Systems. [s. l.]: IEEE, 2006: 402–405.

AGOSTINI L V, SILCA I S, BAMPI S. Pipelined fast 2D DCT architecture for JPEG image compression [C]//14th Synposium on Integrated Circuits and Systems Design. [s. l.]: IEEE, 2001: 226–231.

CHEN H M, LIU W J, LIU T Z, et al. Analysis and architecture design of block matching in BM3D image denoiging [C]//International Conference of Electron Devices and Solid-State Circuits. [s. l.]: IEEE, 2011: 1–2.

CHEN T C, LIAN C J, CHEN L G. Hardware architecture design of an H.264/AVC video code [C]//Asia and South Pacific Conference on Design Automation. [s. l.]: IEEE, 2006: 24–27.

TUAN J C, CHANG T S, JEN C W. On the data reuse and memory bandwidth analysis for full-search block-matching VLSI architecture [J]. IEEE Transactions on Circuits and Systems for Video Technology, 2002, 12(1): 61–72.

CHEN T C, CHIEN S Y, HUANG Y W, et al. Analysis and architecture design of an HDTV720p 30 frames/s H.264/AVC encoder [J]. IEEE Transactions on Circuits and Systems for Video Technology, 2006, 16(6): 673–688.

LIU W J, ZHU Y, LIU T, et al. Analysis and architecture design of aggregation in BM3D [C]//2011 IEEE 9th International Conference on ASIC. Xiamen, China: IEEE, 2011: 703–706.

Author information

Authors and Affiliations

Corresponding author

Additional information

Foundation item: the National Natural Science Foundation of China (No. 61234001)

Rights and permissions

About this article

Cite this article

Zhang, H., Liu, W., Wang, R. et al. Hardware architecture design of block-matching and 3D-filtering denoising algorithm. J. Shanghai Jiaotong Univ. (Sci.) 21, 173–183 (2016). https://doi.org/10.1007/s12204-016-1709-0

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12204-016-1709-0

Keywords

- block-matching and 3D-filtering (BM3D) denoising algorithm

- implementation

- block-matching

- 3Dfiltering

- aggregation