Abstract

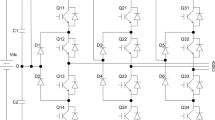

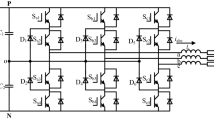

A new modulation approach was presented for the control of neutral-point (NP) voltage variation in the three-level NP-clamped voltage source inverter, and the average NP current model was established based on vector diagram partition. Thus, theory base was built for balancing control of NP potential. Theoretical analysis and experimental results indicate that the proposed method for NP balancing control vector synthesizing concept based can make the average NP current zero, and do not influence NP potential within every sample period. The effectiveness of proposed research approach was verified by simulative and experimental results.

Similar content being viewed by others

References

Wang G Z. Mechanism of DC bus voltage unbalance in diode-clamped multilevel inverter [J]. Proc CSEE, 2002, 22(12): 111–117.

Li Y D. High voltage and large capacity multilevel inverters [M]. Beijing: Scientific Publication, 2005.

Song W X, Chen G C, Wu Hui, et al. A novel SVPWM strategy and its implementation considering neutral-point potential balancing for three-level NPC inverter [J]. Proc CSEE, 2006, 26(12): 95–100.

Song W X, Chen G C, Ding X Y, et al. Research on neutral-point balancing control for three-level NPC inverter based on correlation between carried-based PWM and SVPWM [J]. Trans China Electrotechnical Society, 2005, 20(12): 53–58.

Chen G C. New power electronics converter techniques [M] Beijing: Electric Power Publication, 2005.

Peng F Z. A generalized multilevel inverter topology with self voltage balancing [J]. IEEE Trans Ind Applicat, 2001, 37(5): 611–618.

Lee Y H, Suh B S, Hyun D S. A novel PWM scheme for a three-level voltage source inverter with GTO thyristors [J]. IEEE Trans Ind Applicat, 1996, 32(2): 260–268.

Wei L X, Liu C W, Sun X D, et al. DC voltage balance control method for three-level converter [J]. Journal of Tsinghua University (Science and Technology), 2002, 42(9): 1204–1206 (in Chinese).

Tallam R M, Naik R, Nondahl T A. A carrier-based PWM scheme for neutral-point voltage balancing in three-level inverters [J]. IEEE Trans Ind Applicat, 2005, 41(6): 1734–1743.

Sergio B M, Bordonau J, Boroyevich D, et al. The nearest three virtual space vector PWM—a modulation for the comprehensive neutral-point balancing in the three-level NPC inverter [J]. IEEE Trans Power Electron Lett, 2004, 2(1): 11–15.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Song, Wx., Yao, G., Chen, C. et al. Control method of three-level neutral-point-clamped inverter based on voltage vector diagram partition. J. Shanghai Jiaotong Univ. (Sci.) 13, 457–461 (2008). https://doi.org/10.1007/s12204-008-0457-1

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12204-008-0457-1