Abstract

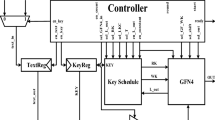

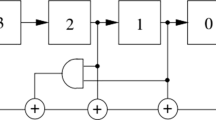

Lightweight cryptography has been one of such fields which is used in resource constrained environments. XXTEA is a popular and efficient lightweight block cipher that can work on minimum 64-bit block size and provides sufficient security as compared to TEA and XTEA block cipher. In this paper, XXTEA lightweight block cipher with 128 bit block size has been used for image encryption by using pipelined hardware architecture which significantly improved the speed with little area overhead. For the hardware architecture of XXTEA, to store the image data, a high level memory interface has been used. The proposed design has been implemented in FPGA and ASIC platforms. The frequency has been improved by 85.9% and has an efficiency of seven time more than the previous literature in FPGA platform. Security analysis has been performed to estimate the security strength of the XXTEA and derived various parameters like histogram, key sensitivity, key space, pixel correlation co-efficient, differential attack, etc.

Similar content being viewed by others

References

Alahdal A and Deshmukh N K 2020 A systematic technical survey of lightweight cryptography on IoT environment. I J S T Research. 9(3)

Kuon I and Rose J 2006 Measuring the gap between FPGAs and ASICs. In: Proceedings of the 2006 ACM/SIGDA14th International Symposium on Field Programmable Gate Arrays pp. 21–30

Wheeler D J and Needham R M 1994 TEA, a tiny encryption algorithm. In: International Workshop on Fast Software Encryption. Springer, pp. 363–366

Kaps J P 2008 Chai-tea, cryptographic hardware implementations of xtea. In: International Conference on Cryptology in India. Springer, pp. 363–375

Chaitra B, Kumar V G K and Shatharama R C 2017 A survey on various lightweight cryptographic algorithms on FPGA. IOSR J. Electron. Commun. Eng. 12(1): 45–59.

Rohmad M S, Saparon A, Amaran H, Arif N and Hashim H 2017 Lightweight block cipher on VHDL. In: 2017 IEEE Symposium on Computer Applications & Industrial Electronics (ISCAIE), pp. 87–90

Anusha R and Veena Devi Shastrimath V 2019 LCBC-XTEA: high throughput lightweight cryptographic block cipher model for low-cost RFID systems. In: Computer Science On-line Conference, pp. 185–196

Khare S and Vishwakarma S K 2014 XXTEA an Optimized Encryption Design with High Feedback Substitution Box Architecture, vol 2

Yeo H Sonh S and Kang M 2020 IP design of corrected block TEA cipher with variable-length message for smart IoT. KSII Transactions on Internet and Information Systems (TIIS) 14: 724–737

Mishra Z, Nath P K and Acharya B 2020 High throughput unified architecture of LEA algorithm for image encryption. Microprocessors and Microsystems. 78: 103214.

Yalla P and Kaps 2009 Compact FPGA implementation of Camellia. In: 2009 International Conference on Field Programmable Logic and Applications, pp. 658–661

Yalla P and Kaps J P 2009 Lightweight cryptography for FPGAs. In: 2009 International Conference on Reconfigurable Computing and FPGAs, pp. 225–230

Soltani A and Sharifian S 2015 An ultra-high throughput and fully pipelined implementation of AES algorithm on FPGA. Microprocessors and Microsystems 7(39): 480–493.

Lara-Nino C A, Diaz-Perez A and Morales-Sandoval M 2017 Lightweight hardware architectures for the present cipher in FPGA. IEEE Transactions on Circuits and Systems I: Regular Papers. 64(9): 2544–2555.

Mishra Z and Acharya B 2020 High throughput and low area architectures of secure IoT algorithm for medical image encryption. Journal of Information Security and Applications. 53: 102533.

Aoki K, Ichikawa T, Kanda M, Matsui M, Moriai S, Nakajima J and Tokita T 2001 Camellia: a 128-bit block cipher suitable for multiple platforms—design andanalysis. In: International Workshop on Selected Areas in Cryptography, pp. 39–56

Shibutani K, Isobe T, Hiwatari H, Mitsuda A, Akishita T and Shirai T 2011 Piccolo: an ultra-lightweight blockcipher. In: International Workshop on Cryptographic Hardware And Embedded Systems, pp. 342–357

Zhang W, Bao Z, Lin D, Rijmen V, Yang B and Verbauwhede I 2015 RECTANGLE: a bit-slice lightweight block cipher suitable for multiple platforms. Science China Information Sciences. 58(12): 1–15.

Wu W and Zhang L 2011 LBlock: a lightweight block cipher. In: International Conference on Applied Cryptography and Network Security. Springer, Berlin, Heidelberg, pp. 327–344

Knudsen L, Leander G, Poschmann A and Robshaw M J 2010 PRINTcipher: a block cipher for IC-printing. In: International Workshop on Cryptographic Hardware and Embedded Systems. Springer, Berlin, Heidelberg, pp. 16–32

Borghoff J, Canteaut A, Güneysu T, Kavun E B, Knezevic M, Knudsen L R, Leander G, Nikov V, Paar C, Rechberger C and Rombouts P 2012 PRINCE–a low-latency block cipher for pervasive computing applications. In: International Conference on the Theory and Application of Cryptology and Information Security. Springer, Berlin, Heidelberg, pp. 208–225

Banik S, Bogdanov A, Isobe T, Shibutani K, Hiwatari H, Akishita T and Regazzoni F 2015 Midori: A block cipher for low energy. In: International Conference on the Theory and Application of Cryptology and Information Security. Springer, Berlin, Heidelberg, pp. 411–436

De Canniere C, Dunkelman O and Knezevic M K 2009 KATANTAN—A family of small and efficient hardware-oriented block ciphers. In: Proceedings of the International Workshop on Cryptographic Hardware and Embeded Systems, Lausanne, Switzerland, pp. 6–9

Hong D, Sung J, Hong S, Lim J, Lee S, Koo B S, Lee C, Chang D, Lee J, Jeong K and Kim H 2006 HIGHT: A new block cipher suitable for low-resource device. In: International Workshop on Cryptographic Hardware and Embedded Systems. Springer, Berlin, Heidelberg, pp. 46–59

Bogdanov A, Knudsen L R, Leander G, Paar C, Poschmann A, Robshaw M J, Seurin Y and Vikkelsoe C 2007 PRESENT: An ultra-lightweight block cipher. In: International Workshop on Cryptographic Hardware and Embedded Systems. Springer, Berlin, Heidelberg, pp. 450–466

Usc-sipi image database[online], http://sipi.usc.edu/Datbase/database.php?volume=misc

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Mishra, Z., Acharya, B. High throughput compact area architecture of XXTEA for IoT application. Sādhanā 48, 80 (2023). https://doi.org/10.1007/s12046-023-02135-x

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12046-023-02135-x