Abstract

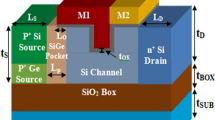

As the devices are getting compact, the size of transistors reduces day by day; however, with certain limitations. Due to miniaturization, the characteristics of the transistor change due to quantum mechanical effects and the present scenario, analytically modeled surface potential-based gate all around (GAA) FET model by solving 1-D Poisson’s equation, approximation method and using necessary boundary condition. Here, the change in channel material (Si, InP, GaAs, InAs and Ge), channel radius (varied from 6 nm to 10 nm), oxide thickness (changed from 2 nm to 5 nm), drain to source voltage (varied from −0.5 V to 0.5 V), Source/Drain doping (varied from 1017 to 1022/cm3) and temperature (from 0 to 300 K) of the transistor, surface potential changes from −1.6 V to 1.3 V approx. respectively, considered as the GAA FET parameters. The proposed novel model exhibits better control over hot carrier effect, Drain Induced Barrier Lowering (DIBL), reduced threshold voltage and other such short channel effects in the GAA FET. Moreover, the I–V characteristics of the GAA FET were analyzed. The MATLAB code is used for modeling of the GAA FET nanowire transistor.

Similar content being viewed by others

References

Moore G E 1998 Cramming more components onto the integrated circuits. (Reprinted from Electronics, pp. 114–117, April 19, 1965) Proceedings of the IEEE 86: 82–85

Young K K 1989 Short-channel effects in fully depleted SOI MOSFETs. IEEE Trans. Electron Devices 36: 399–402

Oh S H, Monroe D and Hergenrother J M 2000 Analytic description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs. IEEE Electron Device Lett. 21: 445–447

Park J T and Colinge J P 2002 Multiple-gate SOI MOSFETs: device design guidelines. IEEE Trans. Electron Devices 49: 2222–2229

Dhiman G and Ghosh P K 2017 Analytical modeling of threshold voltage for double-gate MOSFET. International Conference on Energy, Communication, Data Analytics and Soft Computing (ICECDS), pp. 1584–1588

Wang H, Liu Y, Han G, Shao Y, Zhang C, Feng Q, Zhang J and Hao Y 2017 Performance enhancement in uniaxially strained Germanium–Tin FinTFET: Fin direction dependence. IEEE Trans. Electron Devices 64: 2804–2811

Jagtap S M and Gond V J 2017 Study the performance parameters of novel scale FINFET Device in nm Region. International conference of Electronics, Communication and Aerospace Technology, pp. 424–430

Das S, Choudhury A, Ghosh S, Sarkar S, Chanda M and De S 2017 Parameter modeling of linearly doped double-gate MOSFET with high-k dielectrics. Devices for Integrated Circuit, pp. 136–140

Colinge J P 2007 FinFETs and other multi-gate transistors. Springer.

Hsieh D, Lin J, Kuo P and Chao T 2017 Comprehensive analysis on electrical characteristics of Pi-Gate poly-Si Junctionless FETs. IEEE Trans. Electron Devices 64: 2992–2998

Gupta N, Vohra A and Chaujar R 2016 Linearity performance of Gate Metal Engineered (GME) Omega gate-silicon nanowire MOSFET: a TCAD study. IEEE International Conference on Electron Devices and Solid-State Circuits, pp. 208–211

Samoju V R, Mahapatra K and Tiwari P K 2017 Analytical modeling of subthreshold characteristics by considering quantum confinement effects in ultrathin dual-metal quadruple gate (DMQG) MOSFETs. Superlattices Microstruct. 111: 704–713

Rahman F, Shakya B, Xu X, Forte D and Tehranipoor M 2017 Security beyond CMOS: fundamentals, applications, and roadmap. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 25: 3420–3433

Djeffal F, Ghoggali Z, Dibi Z and Lakhdar N 2009 Analytical analysis of nanoscale multiple-gate MOSFETs including effects of hot-carrier induced interface charges. Microelectron. Reliab. 49: 377–381

Gautam R, Saxena M and Gupta R S 2013 Gate-all-around nanowire MOSFET with catalytic metal gate for gas sensing applications. IEEE Trans. Nanotechnol. 12(6): 932–939

Pandian M K and Balamurugan N B 2014 Analytical threshold voltage modeling of surrounding gate silicon nanowire transistors with different geometries. J. Electr. Eng. Technol. 9: 2079–2088

Kumar M, Haldar S, Gupta M and Gupta R S 2016 Physics-based analytical model for surface potential and subthreshold current of cylindrical Schottky Barrier gate all around MOSFET with high-k gate stack. Superlattices Microstruct. 90: 215–226

Ray B and Mahapatra S 2008 Modeling and analysis of body potential of cylindrical gate-all-around nanowire transistor. IEEE Trans. Electron Devices 55: 2409–2416

Chen X and Tan C M 2014 Modeling and analysis of gate-all-around silicon nanowire FET. Microelectr. Reliab. 54: 1103–1108

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Agarwal, A., Pradhan, P.C. & Swain, B.P. Effects of the physical parameter on gate all around FET. Sādhanā 44, 248 (2019). https://doi.org/10.1007/s12046-019-1232-8

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12046-019-1232-8