Abstract

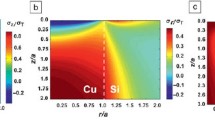

During service, through-silicon vias (TSVs) in vertically stacked-die microelectronic packages are subjected to both thermo-mechanical cycling as well as electromigration. The disparate properties of Cu-filled TSVs and the Si chip induce substantial residual stresses in both components, as well as at the interface. These stresses may drive interfacial sliding with the interface serving as a rapid diffusion path, resulting in significant interfacial strain incompatibilities. In addition, by acting as short-circuit paths for diffusion, the interfaces may carry significant electromigration fluxes, further exacerbating interfacial sliding. The results of recent experiments and modeling are presented to illustrate these effects, and related reliability issues are discussed.

Similar content being viewed by others

References

S. Yoda, N. Kurihara, K. Wakashima, and S. Umekawa, Metall. Trans., 9A (1978), pp. 1229–1236.

I. Dutta, S. Mitra, and A.D. Wiest, Residual Stresses in Composites, ed. E.V. Barrera and I. Dutta (Warrendale, PA: TMS-AIME, 1993), pp. 273–292.

J.V. Funn and I. Dutta, Acta Mater., 47 (1999), pp. 149–164.

R. Nagarajan, I. Dutta, J.V. Funn, and M. Esmele, Mater. Sci. Engng., A259 (1999), pp. 237–252.

I. Dutta, Acta Mater., 48 (2000), pp. 1055–1074.

D.V. Zhmurkin, T.S. Gross, and L.P. Buchwalter, J. Electron. Mater., 26 (1997), p. 791.

S. Ryu, K. Lu, X. Zhang, J. Im, P. Ho, and R. Huang, IEEE Trans. Dev. Mater. Rel., 11(1) (2011), pp. 35–43.

K.A. Peterson, I. Dutta, and M.W. Chen, Acta Mater., 51 (2003), pp. 2831–2846.

I. Dutta, C. Park, K.A. Peterson, J. Vella, and D. Pan, IEEE Trans.-CPMT, 28 (2005), p. 397.

The International Technology Roadmap for Semiconductors (Semiconductor Industry Association, San Jose, CA, 2010 update).

P. Kumar and I. Dutta, Acta Mater., 59 (2011), pp. 2096–2108.

I. De Wolf, IEEE Int. Reliab. Phy. Sym. (Piscataway, NJ: IEEE, 2010), p. 1.

P. Kumar, I. Dutta, and M. S. Bakir, J. Electron. Mater., accepted (July 2011).

http://www.synopsis.com/Community/h./TSV%20Stress%20Management.pdf . (members only access).

N. Khan et al., IEEE Trans.-CPT, 33 (2010), pp. 3–9.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Dutta, I., Kumar, P. & Bakir, M.S. Interface-related reliability challenges in 3-D interconnect systems with through-silicon vias. JOM 63, 70–77 (2011). https://doi.org/10.1007/s11837-011-0179-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11837-011-0179-y