Abstract

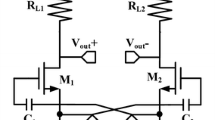

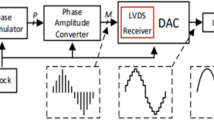

Low Voltage Differential Signaling (LVDS) has become a popular choice for high-speed serial links to conquer the bandwidth bottleneck of intra-chip data transmission. This paper presents the design and the implementation of LVDS Input/Output (I/O) interface circuits in a standard 0.18 μm CMOS technology using thick gate oxide devices (3.3 V), fully compatible with LVDS standard. In the proposed transmitter, a novel Common-Mode FeedBack (CMFB) circuit is utilized to keep the common-mode output voltage stable over Process, supply Voltage and Temperature (PVT) variations. Because there are no area greedy resistors in the CMFB circuitry, the disadvantage of large die area in existing transmitter structures is avoided. To obtain sufficient gain, the receiver consists of three amplifying stages: a voltage amplifying stage, a transconductance amplifying stage, and a transimpedance amplifying stage. And to exclude inner nodes with high RC time constant, shunt-shunt negative feedback is introduced in the receiver. A novel active inductor shunt peaking structure is used in the receiver to fulfill the stringent requirements of high speed and wide Common-Mode Input Region (CMIR) without voltage gain, power dissipation and silicon area penalty. Simulation results show that data rates of 2 Gbps and 2.5 Gbps are achieved for the transmitter and receiver with power consumption of 13.2 mW and 8.3 mW respectively.

Similar content being viewed by others

References

National Semiconductor Corp. LVDS Owner’s Manual, 4th ed., 2008, 7–15.

V. Bratov, J. Binkley, V. Katzman, and J. Choma. Architecture and implementation of a low-power LVDS output buffer for high speed applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 53(2006)10, 2101–2108.

Andrea Boni, Andrea Pierazzi, and Davide Vechi. LVDS I/O interface for Gb/s-per-pin operation in 0.35-μm CMOS. IEEE Journal of Solid-state Circuits, 36(2001)4, 706–711.

Angel Rivera, Elianne Bravo, Manuel Jimenez, and R. Palomera. Design review and innovations in low-voltage differential signaling drivers. Proceedings of IEEE International Midwest Symposium on Circuits and Systems, Hiroshima, Japan, July 25–28, 2004, Vol.3, 339–342.

Hwang Cherng Chow and Wen Wann Sheen. Low power LVDS circuit for serial data communications. Proceedings of IEEE International Symposium on Intelligent Signal Processing and Communication Systems, Hong Kong, Dec. 13–16, 2005, 293–296.

Mingdeng Chen, Jose Silva Martinez, Michael Nix, and M. E. Robinson. Low-voltage low-power LVDS drivers. IEEE Journal of Solid-state Circuits, 40 (2005)1, 472–479.

Chuachin Wang, Jianming Huang, and Jihfon Huang. 1.0 Gbps LVDS transceiver design for LCD panels. Proceedings IEEE Asia-Pacific Conference on Advanced System Integrated Circuits, Fukuoka, Japan, Aug. 4–5, 2004, 236–239.

Gunjan Mandal and Pradip Mandal. Low-power LVDS receiver for 1.3 Gbps physical layer (PHY) interface. Proceedings of IEEE International Symposium on Circuits and Systems, Kobe, Japan, May 23–26, 2005, Vol.3, 2180–2183.

Mingdou Ker and Chienhua Wu. Design on LVDS receiver with new delay-selecting technique for UXGA flat panel display applications. Proceedings of IEEE International Symposium on Circuits and Systems, Island of Kos, Greece, May 21–24, 2006, 5155–5158.

Sudip Shekhar, Jeffrey S. Walling, and David J. Allstot. Bandwidth extension techniques for CMOS amplifier. IEEE Journal of Solid-state Circuits, 41 (2006)11, 2424–2439.

John P. Plasterer, William Michael Lye, and Matthew W. McAdam. System sand methods for actively-peaked current-mode logic. US Patent, 7202706, 2007.

Author information

Authors and Affiliations

Corresponding author

Additional information

Communication author: Wang Xihu, born in 1975, male, Ph.D. candidate.

About this article

Cite this article

Wang, X., Wu, L. & Liu, Y. Low-power LVDS I/O interface for above 2Gb/s-per-pin operation. J. Electron.(China) 26, 525–531 (2009). https://doi.org/10.1007/s11767-008-0066-z

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11767-008-0066-z

Key words

- Input/Output (I/O)

- Low Voltage Differential Signaling (LVDS)

- Transmitter

- Receiver

- Active inductor shunt peaking