Abstract

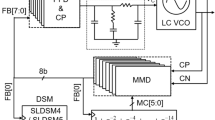

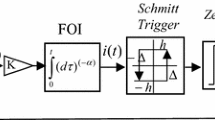

This paper investigates the design of digital Sigma-Delta Modulator (SDM) for fractional-N frequency synthesizer. Characteristics of SDMs are compared through theory analysis and simulation. The curve of maximum-loop-bandwidth vs. maximum-phase-noise is suggested to be a new criterion to the performance of SDM, which greatly helps designers to select an appropriate SDM structure to meet their real application requirements and to reduce the cost as low as possible. A low-spur 3-order Multistage Noise Shaping (MASH)-1-1-1 SDM using three 2-bit first-order cascaded modulators is proposed, which balances the requirements of tone-free and maximum operation frequency.

Similar content being viewed by others

References

B. Miller, B. Conley. A multiple modulator fractional divider. IEEE Trans. on Instrumentation and Measurement, 40(1991)6, 578–593.

T. A. Riley, M. A. Copeland, T. A. Kwasniewski. Delta-sigma modulation in fractional-N frequency synthesis. IEEE Journal of Solid-State Circuits, 28(1993)5, 553–559.

M. H. Perrott, M. D. Trott, C. G. Sodini. A modeling approach for ΔΣ fraction-N frequency synthesizers allowing straightforward noise analysis. IEEE Journal of Solid-State Circuits, 37(2002)8, 1028–1038.

K. Shu, E. Sanchez-Sinencio, F. Maloberti, U. Edun. A comparative study of digital ΔΣ modulators for fractional-N synthesis. Proceedings of IEEE International Conference on Electronics, Circuits and Systems, Malta, 2001, 1391–1394.

L. Sun, T. Lepley, F. Nozahic, A. Bellissant, et al. Reduced complexity, high performance digital delta-sigma modulator for fractional-N frequency synthesis. Proceedings of IEEE International Symposium on Circuits and Systems, Orlando, FL, May–June 1999, vol.2, 152–155.

C.-H. Heng, B.-S. Song. A 1.8-GHz CMOS fractional-N frequency synthesizer with randomized multiphase VCO. IEEE Journal of Solid-State Circuits, 38(2003)6, 848–854.

T. Musch, I. Rolfes, B. Schek. A highly linear frequency ramp generator based on fractional divider phase-locked loop. IEEE Trans. on Instrumentation and Measurement, 48(1999)4, 634–637.

W. Rhee, B.-S. Song, A. Ali. A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order ΔΣ modulator. IEEE Journal of Solid-State Circuits, 35(2000)10, 1453–1460.

B. D. Muer, M. S. J. Steyaert. A CMOS monolithic ΔΣ controlled fractional-N frequency synthesizer for DCS-1800. IEEE Journal of Solid-State Circuits, 37(2002)7, 835–844.

A. M. Fahim, M. I. Elmasry. A wideband sigma-delta phase-locked-loop modulator for wireless applications. IEEE Journal of Solid-State Circuits, 50(2003)2, 53–62.

NC-verilog simulator. http://www.cadence.com/ro-ducts/functional_ver/nc-verilog/index.aspx, downloaded on Feb.21, 2006.

Author information

Authors and Affiliations

Corresponding author

Additional information

Supported in part by the National Natural Science Foundation of China (No. 60025101, No.90207001, and No. 90307016).

Communication author: Mao Xiaojian, born in 1978, male, Ph.D. candidate. Circuits and Systems Division, Department of Electronic Engineering, Tsinghua University, Beijing 100084, China.

About this article

Cite this article

Mao, X., Yang, H. & Wang, H. Comparison of Sigma-Delta Modulator for fractional-N PLL frequency synthesizer. J. of Electron.(China) 24, 374–379 (2007). https://doi.org/10.1007/s11767-005-0208-5

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11767-005-0208-5