Abstract

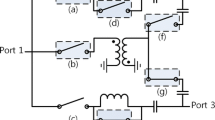

Single-Pole Double-Throw (SPDT) broadband switch has been designed in a 0.25µm Complementary Metal Oxide Semiconductor (CMOS) process. To optimize the performance of isolation and insertion loss, based on normal design, the effects of Gate Series Resistances (GSR) on insertion loss and switching time are analyzed for the first time. The compatible GSRs are chosen by the analyses. The fabricated chips were tested and the results show the switch isolation from DC (Direct Current) to 1GHz exhibits 55dB and insertion loss lower than 2.1dB.

Similar content being viewed by others

References

F. J. Huang, K. K. O. A 0.5-µm T/R switch for 900-MHz wireless applications. IEEE J. Solid-State Circuits, 36(2000)3, 486–492.

I. D. Robertson, S. Lucyszyn. RFIC and MMIC Design and Technology. London, IEE Press, 2001, chapter 8.

P. Gould, J. Lin, et al. NMOS SPDT switch MMIC with >44dB isolation and 30dBm IIP3 for applications within GSM and UMTS bands. Gallium Arsenide Applications Symposium, London, 2001, 24–28.

F. J. Huang, K. K. O. Single-pole double-throw CMOS switches for 900-MHz and 2.4-GHz applications on p-silicon substrates. IEEE J. Solid-State Circuits, 39(2004)1, 35–41.

S. W. Cooper, G. A. Truitt. Voltage-tolerant monolithic L-band GaAs SPDT switch. Microwave Symposium Digest, 1989, 1113–1114.

Author information

Authors and Affiliations

Corresponding author

Additional information

Partially supported by the National Natural Science Foundation of China (No.60501012).

About this article

Cite this article

Han, L., Yang, T., Xie, J. et al. A design of 0.25μm CMOS switch. J. of Electron.(China) 23, 745–747 (2006). https://doi.org/10.1007/s11767-005-0008-y

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11767-005-0008-y