Abstract

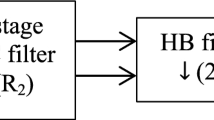

The wide-band digital receiving systems require digital downconversion(DDC) with high data rate and short tuning time in order to intercept the narrow-band signals within broad tuning bandwidth. But these requirements can not be met by the commercial DDC. In this paper an efficient implementation architecture is presented. It combines the flexibility of DFT tuning with the efficiency of the polyphase filter bank decomposition. By first decimating the data prior to filtering and mixing, this architecture gives a better solution to the mismatch between the lower hardware speed and high data rate. The computer simulations show the feasibility of this processing architecture.

Similar content being viewed by others

References

K. D. Zhong, Multirate signal processing. Beijing, Tsinghua University Press, July, 1996, 89–106, (in Chinese).

J. Fudge, M. Legako, C. Sehreiner, An approach to efficient wideband digital downconversion, Proc. ICSPAT, Toronto, Canada, 1998, 713–717.

R. G. Vaughan, N. L. Scott, D. R. White, The theory of bandpass sampling. IEEE Trans. on SP, 39(1991)9, 1973–1984.

R. Baines, The DSP bottleneck. IEEE Communications Magazine, 33(1995)5, 46–54.

D. R. Zahirniak, D. L. Sharpin, T. W. Fields, A hardware-efficient multirate digital channelized receiver architecture. IEEE Trans. on AES, 34(1998)1, 137–151.

Author information

Authors and Affiliations

About this article

Cite this article

Gao, Z., Xiao, X. An efficient implementation architecture for wide-band digital downconversion. J. of Electron.(China) 18, 38–45 (2001). https://doi.org/10.1007/s11767-001-0006-7

Issue Date:

DOI: https://doi.org/10.1007/s11767-001-0006-7