Abstract

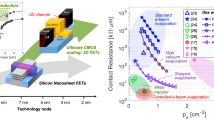

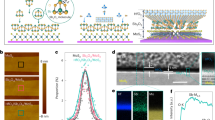

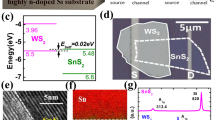

Achieving a low resistance contact is essential for developing two-dimensional (2D) material-based field-effect transistors (FETs). While n-type contacts to 2D semiconductors have been studied, understanding and designs for p-type contacts to 2D semiconductors remain very limited. In this study, we propose and computationally explore three strategies to improve the contact resistance in p-type 2D FETs, which remains a critical bottleneck of 2D logic technology, through the engineering of van der Waals (vdW) material heterostructures: (i) intercalating a graphene layer between a high-work-function metal and 2D semiconductor, which can result in low contact resistance of ~ 60 Ω μm for the graphene-intercalated contact between a high-work-function metal and WSe2 semiconductor; (ii) engineering the atomic stacking order between a vdW metal and 2D semiconductor, which can result in contact resistance of ~ 50 Ω μm; (iii) sandwiching the 2D layered semiconductor between vdW metals from both sides, which can further reduce the contact resistance to ~ 47 Ω μm and ~ 36 Ω μm for cases (i) and (ii), respectively. Experimental fabrication and characterization illustrate the feasibility of structural engineering of contacts. The above structural designs can lead to significantly reduced metal-induced gap states (MIGS) and low barrier height for holes, resulting in low contact resistance. They are also naturally compatible with the gate-all-around (GAA) transistor structure. In addition to contact materials selection, vdW structural design offers an alternative approach for achieving low contact resistance to p-type 2D FETs.

Similar content being viewed by others

Reference

S. Das, A. Sebastian, E. Pop, C.J. McClellan, A.D. Franklin, T. Grasser, T. Knobloch, Y. Illarionov, A.V. Penumatcha, J. Appenzeller, Z. Chen, W. Zhu, I. Asselberghs, L.-J. Li, U.E. Avci, N. Bhat, T.D. Anthopoulos, and R. Singh, Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 7, 786 (2021).

G. Fiori, F. Bonaccorso, G. Iannaccone, T. Palacios, D. Neumaier, A. Seabaugh, S.K. Banerjee, and L. Colombo, Electronics based on two-dimensional materials. Nat. Nanotech. 9, 768 (2014).

X. Liu, M.K. Choi, E.H. Hwang, W.J. Yoo, and J. Sun, Fermi level pinning dependent 2D semiconductor devices: challenges and prospects. Adv. Mater. 34, 2108425 (2022).

A. Allain, J. Kang, K. Banerjee, and A. Kis, Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195 (2015).

D.S. Schulman, A.J. Arnold, and S. Das, Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037 (2018).

P.-C. Shen, C. Su, Y. Lin, A.-S. Chou, C.-C. Cheng, J.-H. Park, M.-H. Chiu, A.-Y. Lu, H.-L. Tang, M.M. Tavakoli, G. Pitner, X. Ji, Z. Cai, N. Mao, J. Wang, V. Tung, J. Li, J. Bokor, A. Zettl, and C.-I. Wu, Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211 (2021).

Y. Lin, P.-C. Shen, C. Su, A. Chou, T. Wu, C. Cheng, J.-H. Park, M.H. Chiu, A. Lu, H. Tang, M.M. Tavakoli, G. Pitner, X. Ji, C. McGahan, X. Wang, Z. Cai, N. Mao, J. Wang, Y. Wang, and W.A. Tisdale, Contact engineering for high-performance N-type 2D semiconductor transistors. 2021 International Electron Devices Meeting (IEDM) (2021), p. 37.2.1–37.2.4

Y. Wang, J.C. Kim, Y. Li, K.Y. Ma, S. Hong, M. Kim, H.S. Shin, H.Y. Jeong, and M. Chhowalla, P-type electrical contacts for 2D transition-metal dichalcogenides. Nature 610, 61 (2022).

M. More, International Roadmap for Devices and Systems (IRDS) (Piscataway: IEEE, 2022), pp.6–10.

R. Wu, Q. Tao, J. Li, W. Li, Y. Chen, Z. Lu, Z. Shu, B. Zhao, H. Ma, Z. Zhang, X. Yang, B. Li, H. Duan, L. Liao, Y. Liu, X. Duan, and X. Duan, Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. Nat. Electron 5, 497 (2022).

N. Yang, Y. Lin, C.-P. Chuu, S. Rahman, T. Wu, A. Chou, S.-L. Liew, K. Fujiwara, H.-Y. Chen, J. Ikeda, A. Tsukazaki, D. Hou, W.-Y. Woon, S.S. Liao, S. Huang, X. Qian, J. Guo, I. Radu, H.-S. Philip Wong, and H. Wang, Computational screening and multiscale simulation of barrier-free contacts for 2D semiconductor pFETs. 2022 International Electron Devices Meeting (IEDM) (2022), p. 28.1.1–28.1.4

G. Kwon, Y.-H. Choi, H. Lee, H.-S. Kim, J. Jeong, K. Jeong, M. Baik, H. Kwon, J. Ahn, E. Lee, and M.-H. Cho, Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 5(4), 241 (2022).

G. Kresse and J. Hafner, Ab initio molecular dynamics for liquid metals. Phys. Rev. B 47, 558 (1993).

G. Kresse and J. Hafner, Ab initio molecular-dynamics simulation of the liquid-metal–amorphous-semiconductor transition in germanium. Phys. Rev. B 49, 14251 (1995).

G. Kresse and J. Furthmüller, Efficiency of ab-initio total energy calculations for metals and semiconductors using a plane-wave basis set. Comput. Mat. Sci. 6, 15 (1996).

G. Kresse and J. Furthmüller, Electronic structure of two-dimensional crystals from ab initio theory. Phys. Rev. B 54, 11169 (1996).

J. Klimeš, D.R. Bowler, and A. Michaelides, Van der Waals density functionals applied to solids. Phys. Rev. B 83, 195131 (2011).

G. Kresse and D. Joubert, From ultrasoft pseudopotentials to the projector augmented-wave method. Phys. Rev. 59, 1758 (1999).

S. Banerjee, L. Cao, Y.S. Ang, L.K. Ang, and P. Zhang, Reducing contact resistance in two-dimensional-material-based electrical contacts by roughness engineering. Phys. Rev. Appl. 13(6), 064021 (2020).

N. Yang, Y. Lin, C.-P. Chuu, M. Rahman, T. Wu, A. Chou, H.-Y. Chen, W.-Y. Woon, S.S. Liao, S. Huang, X. Qian, J. Guo, I. Radu, H.-S. Philip Wong, and H. Wang, Ab Initio computational screening and performance assessment of van der Waals and Semimetallic contacts to monolayer WSe2 P-type field-effect transistors. IEEE Trans. Electron Devices 70(4), 2090 (2023).

A. Tunga, Z. Zhao, A. Shukla, W. Zhu, and S. Rakheja, Physics-based modeling and validation of 2-D Schottky barrier field-effect transistors. IEEE Trans. Electron Devices 70(4), 2034 (2023).

S. Conti, D. Neilson, F.M. Peeters, and A. Perali, Transition metal dichalcogenides as strategy for high temperature electron-hole superfluidity. Condens. Matter 5(1), 22 (2020).

L. Liu, S.B. Kumar, Y. Ouyang, and J. Guo, Performance limits of monolayer transition metal dichalcogenide transistors. IEEE Trans. Electron Devices 58(9), 3042 (2011).

J. Guo, S. Datta, M. Lundstrom, and M.P. Anantam, Toward multiscale modeling of carbon nanotube transistors. Int. J. Multiscale Comput. Eng. 2, 257 (2004).

L. Yang and J. Guo, Role of dissipative quantum transport in DC, RF, and self-heating characteristics of short channel graphene FETs. 2011 International Electron Devices Meeting (IEDM) (2011), p. 11.5.1–11.5.4

Y. Taur and T.H. Ning, Fundamentals of Modern VLSI Devices (New York: Cambridge University Press, 2022), pp.274–277.

A. Allain and A. Kis, Electron and hole mobilities in single-layer WSe2. ACS Nano 8(7), 7180 (2014).

H. Cho, M. Sritharan, Y. Ju, P. Pujar, R. Dutta, W. Jang, Y. Kim, S. Hong, Y. Yoon, and S. Kim, Se-vacancy healing with substitutional oxygen in WSe2 for high-mobility p-type field-effect transistors. ACS Nano 17(12), 11279 (2023).

Acknowledgments

This work was supported by NSF grants ECCS-2203625, 1904580, 1653870 and ARO grant W911NF1810268.

Funding

National Science Foundation (2203625, 1904580, 1653870), Army Research Office (W911NF1810268).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Yang, N., Hsu, TH., Chen, HY. et al. Van der Waals Heterostructure Engineering for Ultralow-Resistance Contact in 2D Semiconductor P-Type Transistors. J. Electron. Mater. 53, 2150–2161 (2024). https://doi.org/10.1007/s11664-024-10920-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-024-10920-5