Abstract

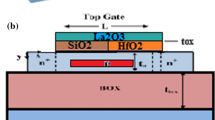

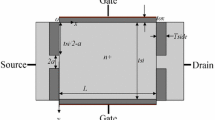

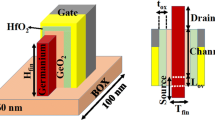

Modeling a stacked-gate core–shell (C-S) junctionless (JL) DG-FET and examining its suitability for low-power applications are the primary focus of the present paper. Here, charge-based analytical 2D modeling is adopted to determine the surface potential, threshold voltage, drain current and drain-induced barrier lowering (DIBL) for various core/shell thickness and shell dopant density values. The analytical model is calibrated with the experimental data available in literature, and the analytical results closely match those obtained from device simulation by Silvaco ATLAS. Next, a comparative analysis is made for C-S-JL-FET, JAM-JL-FET and traditional JL-FET, on the basis of their analog figures of merit (FOMs) [drain current (\(I_d\)), transconductance generation factor (\(g_m/I_d\)), intrinsic gain (\(g_m/g_d\)), total gate capacitance (\(C_{\mathrm{{gg}}}\)) and Early voltage (\(V_{\mathrm{{EA}}}\))], and linearity FOMs [input power at the third-order intercept point (\(P_{\mathrm{{IP}}3}\)), second-order voltage intercept point (\(V_{\mathrm{{IP}}2}\)), third-order voltage intercept point (\(V_{\mathrm{{IP}}3}\)) and third-order intermodulation distortion (\(\mathrm{{IMD3}}\))]. The performance of a cascode amplifier is also examined. The entire study reveals that all the \(g_m/I_d\) ratio, \(V_{\mathrm{{EA}}}\) and intrinsic gain are largest, along with significantly small OFF-current, for the C-S-JL-FET. It also offers maximum bandwidth with significantly high gain while used in a cascode amplifier. Thus, the C-S-JL-FET appears as a very promising potential candidate for low-power applications.

Similar content being viewed by others

Data Availability

Authors are not willing to disclose the data and materials related to this research.

Code Availability

Authors are not willing to disclose the code.

References

C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti Akhavan, P. Razavi, and J.-P. Colinge, High-temperature performance of silicon junctionless MOSFETs. IEEE Trans. Electron Devices 57, 620 (2010).

C.-W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, and J.P. Colinge, Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94, 053511 (2009).

Y. Xiao, B. Zhang, H. Lou, L. Zhang, and X. Lin, A compact model of subthreshold current with source/drain depletion effect for the short-channel junctionless cylindrical surrounding-gate mosfets. IEEE Trans. Electron Devices 63, 2176 (2016).

J.-P. Colinge, A. Kranti, R. Yan, I. Ferain, N.D. Akhavan, P. Razavi, C.-W. Lee, R. Yu, and C. Colinge, A simulation comparison between junctionless and inversion-mode mugfets. ECS Trans. 35, 63 (2011).

Y. Xiao, X. Lin, H. Lou, B. Zhang, L. Zhang, and M. Chan, A short channel double-gate junctionless transistor model including the dynamic channel boundary effect. IEEE Trans. Electron Devices 63, 4661 (2016).

X. Jin, X. Liu, M. Wu, R. Chuai, J.-H. Lee, and J.-H. Lee, Modelling of the nanoscale channel length effect on the subthreshold characteristics of junctionless field-effect transistors with a symmetric double-gate structure. J. Phys. D Appl. Phys. 45, 375102 (2012).

A. Gnudi, S. Reggiani, E. Gnani, and G. Baccarani, Semianalytical model of the subthreshold current in short-channel junctionless symmetric doublegate field-effect transistors. IEEE Trans. Electron Devices 60, 1342 (2013).

J.-P. Colinge, C.-W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, Nanowire transistors without junctions. Nat. Nanotechnol. 5, 225 (2010).

S.Y. Kim, J.H. Seo, Y.J. Yoon, G.M. Yoo, Y.J. Kim, H.R. Eun, H.S. Kang, J. Kim, S. Cho, and J.H. Lee, Kang IM design and analysis of sub-10 nm junctionless finshaped field-effect transistors. Inst. Electron. Eng. Korea 14, 508 (2014).

S. Sahay and M.J. Kumar, Symmetric operation in an extended back gate JLFET for scaling to the 5-nm regime considering quantum confinement effects. IEEE Trans. Electron Devices 64, 21 (2017).

P.-J. Sung, T.-C. Cho, F.-J. Hou, F.-K. Hsueh, S.-T. Chung, Y.-J. Lee, M.I. Current, and T.-S. Chao, High-performance uniaxial tensile strained n-channel JL SOI FETs and triangular JL bulk FinFETs for nanoscaled applications. IEEE Trans. Electron Devices 64, 2054 (2017).

A. Chattopadhyay, C.K. Sarkar, and C. Bose, Compact analytical modelling of underlap gate stack graded channel junction accumulation mode junctionless FET in subthreshold regime. Superlattices Microstruct. 162, 107110 (2022).

N. Trivedi, M. Kumar, S. Haldar, S.S. Deswal, M. Gupta, and R.S. Gupta, Analytical modeling simulation and characterization of short channel junctionless accumulation mode surrounding gate (JLAMSG) MOSFET for improved analog/RF performance. Superlattices Microstruct. 100, 1263 (2016).

Y.-J. Lee, T.-C. Cho, S.-S. Chuang, F.-K. Hsueh, Y.-L. Lu, P.-J. Sung, H.-C. Chen, M.I. Current, T.-Y. Tseng, T.-S. Chao, C. Hu, and F.-L. Yang, Low-temperature microwave annealing processes for future IC fabrication review. IEEE Trans. Electron Devices 61, 651 (2014).

J.C. Ho, R. Yerushalmi, Z.A. Jacobson, Z. Fan, R.L. Alley, and A. Javey, Controlled nanoscale doping of semiconductors via molecular monolayers. Nat. Mater. 7, 62 (2008).

J.C. Ho, R. Yerushalmi, G. Smith, P. Majhi, J. Bennett, J. Halim, V.N. Faifer, and A. Javey, Wafer-scale, sub-5 nm junction formation by monolayer doping and conventional spike annealing. Nano Lett. 9, 725 (2009).

Y.-J. Lee, T.-C. Cho, K.-H. Kao, P.-J. Sung, F.-K. Hsueh, P.-C. Huang, C.-T. Wu, S.-H. Hsu, W.-H. Huang, H.-C. Chen, Y. Li, M.I. Current, B. Hengstebeck, Marino J., T. B¨uy¨uklimanli, J.-M. Shieh, T.-S. Chao, W.-F. Wu, W.-K. Yeh, A novel junctionless finfet structure with sub-5 nm shell doping profile by molecular monolayer doping and microwave annealing. in 2014 IEEE International Electron Devices Meeting, pp. 32–71 (2014)

M.P.V. Kumar, C.-Y. Hu, K.-H. Kao, Y.-J. Lee, and T.-S. Chao, Impacts of the shell doping profile on the electrical characteristics of junctionless FETS. IEEE Trans. Electron Devices 62, 3541 (2015).

N. Jaiswal and A. Kranti, Modeling short-channel effects in core–shell junctionless MOSFET. IEEE Trans. Electron Devices 66, 292 (2019).

C.R. Manoj and V.R. Rao, Impact of high-k gate dielectrics on the device and circuit performance of nanoscale finfets. IEEE Electron Device Lett. 28, 295 (2007).

W. Zhu, J.-P. Han, and T.P. Ma, Mobility measurement and degradation mechanisms of MOSFETs made with ultrathin high-k dielectrics. IEEE Trans. Electron Devices 51, 98 (2004).

P. Magnone, F. Crupi, G. Giusi, C. Pace, E. Simoen, C. Claeys, L. Pantisano, D. Maji, V.R. Rao, and P. Srinivasan, 1/f noise in drain and gate current of MOSFETs with high-k gate stacks. IEEE Trans. Device Mater. Reliab. 9, 180 (2009).

B. Cheng, M. Cao, R. Rao, A. Inani, P. Vande Voorde, W.M. Greene, J.M.C. Stork, Z. Yu, P.M. Zeitzoff, and J.C.S. Woo, The impact of high-/spl kappa/ gate dielectrics and metal gate electrodes on sub-100 nm MOSFETs. IEEE Trans. Electron Devices 46, 1537 (1999).

Y.-J. Lee, T.-C. Cho, P.-J. Sung, K.-H. Kao, F.-K. Hsueh, F.-J. Hou, P.-C. Chen, H.-C. Chen, C.-T. Wu, S.-H. Hsu, Y.-J. Chen, Y.-M. Huang, Y.-F. Hou, W.-H. Huang, C.-C. Yang, B.-Y. Chen, K.-L. Lin, M.-C. Chen, C.-H. Shen, G.-W. Huang, K.-P. Huang, M.I. Current, Y. Li, S. Samukawa, W.-F. Wu, J.-M. Shieh, T.-S. Chao, W.-K. Yeh, High performance poly si junctionless transistors with sub-5nm conformally doped layers by molecular monolayer doping and microwave incorporating CO2 laser annealing for 3d stacked Ics applications. in 2015 IEEE International Electron Devices Meeting (IEDM), pp. 6–21 (2015)

J.-M. Sallese, N. Chevillon, C. Lallement, B. Iniguez, and F. Pregaldiny, Charge-based modeling of junctionless double-gate field-effect transistors. IEEE Trans. Electron Devices 58, 2628 (2011).

J.P. Duarte, S.-J. Choi, and Y.-K. Choi, A full-range drain current model for double-gate junctionless transistors. IEEE Trans. Electron Devices 58, 4219 (2011).

S. Rewari, V. Nath, S. Haldar, S.S. Deswal, and R.S. Gupta, Improved analog and ac performance with increased noise immunity using nanotube junctionless field effect transistor (NJLFET). Appl. Phys. A 12, 1–10 (2016).

A. Chattopadhyay, M. Chanda, C. Bose, and C.K. Sarkar, Analytical modelling of linearity and intermodulation distortion of 3d gate all around junctionless (GAA—Jl) FET. Superlattices Microstruct. 150, 106788 (2021).

S. Kaya and W. Ma, Optimization of RF linearity in DG-MOSFETs. IEEE Electron Device Lett. 25, 308 (2004).

N.D. Arora and G.S. Gildenblat, A semi-empirical model of the MOSFET inversion layer mobility for low-temperature operation. IEEE Trans. Electron Devices 34, 89 (1987).

C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans. Comput.-Aid. Des. Integr. Circuits Syst. 7, 1164 (1988).

D. Gola, B. Singh, and P.K. Tiwari, Subthreshold modeling of tri-gate junctionless transistors with variable channel edges and substrate bias effects. IEEE Trans. Electron Devices 65, 1663 (2018).

Funding

No funding is available for this work.

Author information

Authors and Affiliations

Contributions

AC: conceptualization, methodology, software, data curation, writing—original draft preparation, reviewing. CB: supervision, correction of manuscript, reviewing and editing.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Ethical Approval

For this type of study formal consent is not required.

Consent to Participate

Not applicable for this type of study.

Consent for Publication

Not applicable for this type of study.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Chattopadhyay, A., Bose, C. Investigation of Core–Shell Junctionless Gate-Stack DG-FET in Low-Power Applications Using Charge-Based Modeling. J. Electron. Mater. 53, 157–170 (2024). https://doi.org/10.1007/s11664-023-10742-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-023-10742-x