Abstract

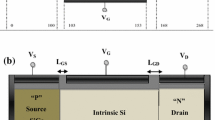

In this study, the analog and radio frequency (RF) functionality of an indium arsenide-gallium antimonide (InAs-GaSb) tunnel field-effect transistor (TFET) with an InAs pocket layer is examined. The potential advantages and disadvantages of TFETs in comparison to their traditional counterparts are thoroughly analyzed. The conductivity of the channel is modulated by an InAs pocket layer. The InAs-GaSb vertical TFET (VTFET) with an InAs pocket layer (device B) yields higher ON-current (6.39 × 10−6 A/μm) compared to the InAs-GaSb VTFET (device A) (5.18 × 10−8 A/μm). Additionally, device B offers low OFF-current (2.26 × 10−17 A/μm) compared with device A (1.14 × 10−16 A/μm). The channel resistance values are 2 × 10−5 Ω·cm for device B and 5 × 10−3 Ω·cm for device A. The transconductance (gm) values for device B and device-A are 0.78 mS/μm and 0.37 mS/μm, respectively. Device B has a cutoff frequency (fT) of 37 GHz whereas that for device A is only 22 GHz at VGS = 0.6 V. Compared to standard TFETs, the fT of the proposed design is 15 GHz higher owing to increased transconductance. The ON-state loss can be reduced by lowering the channel resistance. The InAs pocket layer in InAs-GaSb VTFETs makes them ideal candidates for low-power RF and analog applications.

Similar content being viewed by others

Data Availability

Not applicable.

Code Availability

Not applicable.

References

S.O. Koswatta, M.S. Lundstrom, and D.E. Nikonov, Performance comparison between p-i-n tunneling transistors and device-a MOSFETs. IEEE Trans. Electron Dev. 56, 456 (2009).

M. Saravanan and E. Parthasarathy, A review of III-V tunnel field effect transistors for future ultra-low power digital/analog applications. Microelectron. J. 114, 105102 (2021).

M. Zare, F. Peyravi, and S.E. Hosseini, Impact of hetero-dielectric ferroelectric gate stack on analog/RF performance of tunnel FET. J. Electron. Mater. 49, 5638 (2020).

S. Yadav, B. Awadhiya, and A. Mittal, Ohmic Junction based tunnel FET for high frequency and low power applications. Silicon 24, 74 (2022).

A.M. Ionescu and H. Riel, Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329 (2011).

S. Vidhyadharan, R. Yadav, S. Hariprasad, and S.S. Dan, An innovative ultra-low voltage GOTFET based regenerative-latch Schmitt trigger. Microelectron. J. 104, 104879 (2020).

W.Y. Choi, B.-G. Park, J.D. Lee, and T.-J.K. Liu, Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Dev. Lett. 28(8), 743 (2007).

P. Sharma, J. Madan, R. Pandey, and R. Sharma, RF analysis of double-gate junctionless tunnel FET for wireless communication systems: a non-quasi static approach. J. Electron. Mater. 50, 138 (2021).

J. Wu and Y. Taur, Reduction of TFET off-current and subthreshold swing by lightly doped drain. IEEE Trans. Electron Dev. 63(8), 3342 (2016).

Q. Zhang, W. Zhao, and A. Seabaugh, Low-subthreshold-swing tunnel transistors. IEEE Electron. Dev. Lett. 27, 297 (2006).

K.K. Bhuwalka, J. Schulze, and I. Eisele, Performance enhancement of vertical tunnel field-effect transistor with SiGe in the p+ layer. Jpn. J. Appl. Phys. 43(7A), 4073 (2004).

P.-F. Wang, K. Hilsenbeck, T. Nirschl, M. Oswald, C. Stepper, M. Weiss, D. Schmitt-Landsiedel, and W. Hansch, Complementary tunneling transistor for low power applications. Solid State Electron. 48(12), 2281 (2004).

J. Appenzeller, Y.-M. Lin, J. Knoch, and P. Avouris, Band-to-band tunneling in carbon nanotube field-effect transistors. Phys. Rev. Lett. 93(19), 196805–196811 (2004).

J.H. Park, G.S. Jang, H.Y. Kim, K.H. Seok, H. Chae, and J.S.K. Lee, Sub-kT/q subthreshold-slope using negative capacitance in low-temperature polycrystalline-silicon thin-film transistor. Sci. Rep. 6, 24734 (2016).

A. Pon, A. Bhattacharyya, and R. Ramesh, Charge plasma-based phosphorene tunnel FET using a hybrid computational method. J. Electron. Mater. Lett. 50, 3624 (2021).

S. Hussain, N. Mustakim, and J.K. Saha, Linearity performance and distortion analysis of carbon nanotube tunneling FET. J. Electron. Mater. 50, 1496 (2021).

B. Sedighi, X.S. Hu, H. Liu, J.J. Nahas, and M. Niemier, Analog circuit design using tunnel FETs. IEEE Trans. Circuits Syst. I Regul. Pap. 62, 39 (2015).

D. Cavalheiro, F. Moll, and S. Valtchev, TFET-based power management circuit for RF energy harvesting. IEEE J. Electron. Dev. Soc. 5(1), 7 (2017).

F. Settino, M. Lanuzza, S. Strangio, F. Crupi, P. Palestri, D. Esseni, and S. Luca, Understanding the potential and limitations of tunnel FET for low-voltage analog/mixed-signal circuits. IEEE Trans. Electron. Dev. 64(6), 2736 (2017).

E.O. Kane, Theory of tunneling. J. Appl. Phys. 32(1), 83 (1961).

J.E. Harvey, Fourier treatment of near-field scalar diffraction theory. Am. J. Phys. 47(11), 974 (1979).

B. Anjana, K. Pradeep, R. Balwinder, and A. Sunny, Design and performance optimization of dopingless vertical nanowire TFET using gate stacking technique. Science 51, 4005 (2022).

Y. Shao, M. Pala, D. Esseni, and J.A. del Alamo, Scaling of GaSb/InAs vertical nanowire Esaki diodes down to sub-10-nm diameter. IEEE Trans. Electron. Dev. 69, 4 (2022).

G.A.M. Hurkx, D.B.M. Klaasen, M.P.G. Knuvers, and F.G. Ohara, A new recombination model describing heavy-doping effects and low-temperature behaviour. IEDM Tech. Digest. 307, 758 (1989).

B.R. Raad, D. Sharma, K. Nigam, and P. Kondekar, Physics-based simulation study of high-performance gallium arsenide phosphide indium gallium arsenide tunnel field-effect transistor. IET Micro. Nano Lett. 11(7), 366 (2016).

T. Chawla, and B. Raj, Design and simulation of triple metal double-gate germanium on insulator vertical tunnel field effect transistor. Microelectron. J. 114, 105125 (2021).

A. Schenk, A model for the field and temperature dependence of Shockley–Read–Hall lifetimes in silicon. Solid-State Electron. 35(11), 1585 (1992).

W.K. Hyun, and K. Daewoong, Low-power vertical tunnel field-effect transistor ternary inverter. J. Electron Dev. Soc. 9, 286 (2021).

H. Yuanyuan, Z. Lipeng, Z. Qiyi, G. Yaohui, R. Zhaoyu, B. Jintao, and X. Xinlong, Surface optical rectification from layered MoS2 crystal by THz time-domain surface emission spectroscopy. Am. Chem. Soc. 9(5), 4956 (2017).

T.A. Bhat, M. Mustafa, and M.R. Beigh, Study of short channel effects in n-FinFET structure for Si, GaAs, GaSb and GaN channel materials. J. Nano- Electron. Phys. 7, 03010 (2015).

S. Tirkey, D. Sharma, D.S. Yadav, and S. Yadav, Analysis of a novel metal implant junctionless tunnel FET for Better DC and Analog/RF electrostatic parameters. IEEE Trans. Electron Dev. 64, 9 (2017).

P. Ghosh, S. Haldar, R.S. Gupta, and M. Gupta, An investigation of linearity performance and intermodulation distortion of GME CGT MOSFET for RFIC design. IEEE Trans. Electron Dev. 59(12), 3263 (2012).

A.K. Singh, M.R. Tripathy, K. Baral, P.K. Singh, and S. Jit, Investigation of DC, RF and linearity performances of a back-gated (BG) heterojunction (HJ) TFET-on-selbox-substrate (STFET): introduction to a BG-HJ-STEFT based CMOS inverter. Microelectron. J. 102, 104775 (2021).

Acknowledgments

The authors acknowledge the SRM Institute of Science and Technology, Chennai, India, for providing the support and facility to carry out this research work.

Funding

Not applicable.

Author information

Authors and Affiliations

Contributions

All work in this paper was performed jointly by MS and EP.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest reported in this paper.

Consent to Participate

Not applicable.

Consent for Publication

Not applicable as the manuscript does not contain any data from individuals.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Saravanan, M., Parthasarathy, E. Impact of Pocket Layer on Linearity and Analog/RF Performance of InAs-GaSb Vertical Tunnel Field-Effect Transistor. J. Electron. Mater. 52, 2772–2779 (2023). https://doi.org/10.1007/s11664-023-10239-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-023-10239-7