Abstract

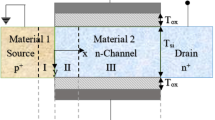

A double-gate heterojunction negative-capacitance tunnel field-effect transistor is proposed for OFF-current reduction with the help of a dual-material gate. In the proposed structure, the gate oxide is a layered arrangement of high-κ dielectric over low-κ dielectric to increase gate control and to eliminate lattice mismatch issues. The tangent line approximation approach is utilized in both the source-channel region and the channel-drain region to precisely model the drain current. The model is validated using two-dimensional simulations of the double-gate heterojunction dual-material gate tunnel field-effect transistor using the one-dimensional (1-D) Landau–Khalatnikov equation. The proposed topology also exhibits improvements in sub-threshold swing, ON–OFF drain current ratio, and output characteristics. The model precisely matches the device simulator results.

Similar content being viewed by others

References

J.M. Kumar, R. Vishnoi, and P. Pandey, Tunnel Field-Effect Transistors (TFET) Modelling and Simulation (Wiley, Heidelberg, 2016)

S. Sahoo, S. Dash, S. Routray, and G. Mishra, Performance improvement of heterojunction double gate TFET with Gaussian doping. Silicon 13(12), 4275–4283 (2020)

S. Ahish, D. Sharma, N. Kumar, Y. Balachandra, and M.H. Vasantha, Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Trans. Electron Devices 63(1), 288–295 (2016)

Y. Guan, Z. Li, W. Zunchao, and Y. Zhang, An accurate analytical current model of double-gate heterojunction tunneling FET. IEEE Trans. Electron Devices 64(3), 938–944 (2017)

H.F. Xu and B.G. Guan, Two-dimensional analytical model for hetero-junction double-gate tunnel field-effect transistor with a stacked gate-oxide structure. Jpn. J. Appl. Phys. 56(5), 054201 (2017)

S. Kumar, E. Goel, K. Singh, M.B. Kumar, and S. Jit, A compact 2-D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a \(\text{ sio}_{{2}}\)/high-k stacked gate-oxide structure. IEEE Trans. Electron Devices 63(8), 3291–3299 (2016)

S. Su, R.K. James, J. Jacob, and A. Pradeep, Enhancement and modeling of drain current in negative capacitance double gate TFET. Silicon 14, 6157–6167 (2021)

S. Saurabh and M.J. Kumar, Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

P. Pandey, R. Vishnoi, and M.J. Kumar, A full-range dual material gate tunnel field effect transistor drain current model considering both source and drain depletion region band-to-band tunneling. J. Comput. Electron. 14(1), 280–287 (2015)

S.L. Noor, S. Safa, and M.Z. Khan, Dual-material double-gate tunnel FET: gate threshold voltage modeling and extraction. J. Comput. Electron. 15(3), 763–769 (2016)

S. Kumar, K. Singh, K. Nigam, V.A. Tikkiwal, and B. Chandan, Dual-material dual-oxide double-gate TFET for improvement in DC characteristics, analog-RF and linearity performance. Appl. Phys. A 125(5), 1–8 (2019)

N. Chowdhury, S.F. Azad, and Q.D. Khosru, Negative capacitance tunnel field effect transistor: a novel device with low subthreshold swing and high on current. ECS Trans. 58, 1 (2014)

S. Salahuddin and S. Datta, Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8(2), 405–410 (2008)

N. Chowdhury, I. Ahmed, T. Fakhrul, M.K. Alam, and Q.D.M. Khosru, A low subthreshold swing tunneling field effect transistor for next generation low power CMOS applications. Phys. E Low-Dimens. Syst. Nanostruct. 74, 251–257 (2015)

H. Xu and Y. Dai, Two-dimensional analytical model of double-gate tunnel FETs with interface trapped charges including effects of channel mobile charge carriers. J. Semicond. 38(2), 024004 (2017)

C. Jiang, R. Liang and J. Xu, Investigation of negative capacitance gate-all-around tunnel FETs combining numerical simulation and analytical modeling. IEEE Trans. Nanotechnol. 16(1), 58–67 (2017)

A. Singh, M. Sajad, A. Singh, N. Kumar, S.I. Amin, and S. Anand, Design and analysis of negative capacitance based dual material dopingless tunnel FET. Superlattices Microstruct. 156, 106964 (2021)

N. Thoti and Y. Li, Design of GAA nanosheet ferroelectric area tunneling FET and its significance with DC/RF characteristics including linearity analyses. Nanoscale Res. Lett. 17(1), 1–11 (2022)

S. Kamaei, A. Saeidi, C. Gastaldi, T. Rosca, L. Capua, M. Cavalieri, and A.M. Ionescu, Gate energy efficiency and negative capacitance in ferroelectric 2D/2D TFET from cryogenic to high temperatures. npj 2D Mater. Appl. 5(1), 1–10 (2021)

E.O. Kane, Zener tunneling in semiconductors. J. Phys. Chem. Solids 12(2), 181–188 (1960)

V. AA, K. MK, S. SP, and J. Jacob, Drain current modeling of tunnel FET using Simpson’s rule. Silicon 14(11), 5931–5939 (2021)

H. Xu, Two dimensional analytical model for a negative capacitance double gate tunnel field effect transistor with ferroelectric gate dielectric. J. Semicond. 39(10), 104004 (2018)

I.H. Smaili, Design and Simulation of Short Channel Si:HfO2 Ferroelectric Field Effect Transistor (FEFET) (Rochester Institute of Technology, Newyork, 2014)

J. Muller, P. Polakowski, S. Mueller, and T. Mikolajick, Ferroelectric hafnium oxide based materials and devices: assessment of current status and future prospects. ECS J. Solid State Sci. Technol. 4(5), 30–35 (2015)

T. Mittmann, M. Michailow, P.D. Lomenzo, J. Gartner, M. Falkowski, A. Kersch, and U. Schroeder, Stabilizing the ferroelectric phase in HfO2-based films sputtered from ceramic targets under ambient oxygen. Nanoscale 13, 912–921 (2021)

S.A. Samuel and N.B. Balamurugan, An analytical modeling and simulation of dual material double gate tunnel field effect transistor for low power applications. J. Electr. Eng. Technol. 9, 247–253 (2014)

C. Nuñez, H. Luisier, and M.A. Schenk, Analysis of InAs-Si heterojunction nanowire tunnel FETS: Extreme confinement vs bulk. In: 2014 44th European Solid State Device Research Conference (ESSDERC), pp. 118–119 (2014)

Author information

Authors and Affiliations

Contributions

SUS: Conceptualization, Writing – original draft, Methodology. BK: Investigation, Writing – original draft. HH: Investigation, Writing – original draft. JJ: Conceptualization, Writing – review and editing. AP: Supervision, Writing – review and editing. RKJ: Writing – review and editing, Supervision

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Shikha, U.S., Krishna, B., Harikumar, H. et al. OFF Current Reduction in Negative Capacitance Heterojunction TFET. J. Electron. Mater. 52, 2695–2707 (2023). https://doi.org/10.1007/s11664-023-10232-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-023-10232-0