Abstract

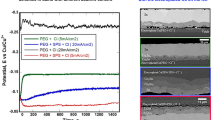

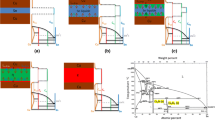

The behavior of void growth in ultra-large-scale integration Cu interconnections has been investigated by grain-boundary diffusion simulation to confirm the effectiveness of the high-pressure reflow process for suppressing stress-induced voiding. Void growth was simulated by combining stress analysis and atomic flux analysis. The former was calculated by the finite-element method (FEM), and the latter was calculated by an unusual FEM in which grain boundaries were defined as elements. From the results of void growth analysis, we found that voids tend to disappear during the isochronal annealing step and that the void shrinkage rate can be increased by two to three times by applying pressure of 150 MPa compared with normal-pressure annealing. From the simulation results, it can be conjectured that the high-pressure reflow process is effective for eliminating voids in via holes of Cu interconnections.

Similar content being viewed by others

References

P. Singer, Semiconductor International November 1997 (1997), pp. 67–70.

P. Gwynne, IBM Research No. 4, 1997 (1997), pp. 17–22.

A.E. Braun, Semiconductor International April 1999 (1999), pp. 58–66.

B. Li, T.D. Sullivan, T.C. Lee, and D. Badami, Microelectron. Reliab. 44, 365 (2004).

K. Abe, Y. Harada, M. Yoshimaru, and H. Onoda, J. Vac. Sci. Technol. B 22, 721 (2004).

T.C. Wang, T.E. Hsieh, M.T. Wang, D.S. Su, C.H. Chang, Y.L. Wang, and J.Y. Lee, J. Electrochem. Soc. 152, G45 (2005).

M.H. Lin, Y.L. Lin, K.P. Chang, K.C. Su, and T. Wang, Jpn. J. Appl. Phys. 45, 700 (2006).

H. Tsuchikawa, Y. Mizushima, T. Nakamura, T. Suzuki, and H. Nakajima, Jpn. J. Appl. Phys. 45, 714 (2006).

T. Ohshima, K. Hinode, H. Yamaguchi, H. Aoki, K. Torii, T. Saito, K. Ishikawa, J. Noguchi, M. Fukui, T. Nakamura, S. Uno, K. Tsugane, J. Murata, K. Kikushima, H. Sekisaka, E. Murakami, K. Okuyama, and T. Iwasaki, Proceedings of the 2002 IEEE International Electron Devices Meeting (San Francisco, 2002), pp. 757–760.

K. Yoshida, T. Fujimaki, K. Miyamoto, T. Honma, H. Kaneko, H. Nakazawa, and M. Morita, Proceedings of the 2002 IEEE International Electron Devices Meeting (San Francisco, 2002), pp. 753–756.

M. Ueki, M. Hiroi, N. Ikarashi, T. Onoda, N. Furutake, M. Yoshiki, and Y. Hayashi, Proceedings of the 2002 IEEE International Electron Devices Meeting (San Francisco, 2002), pp. 749–752.

E.T. Ogawa, J.W. McPherson, J.A. Rosal, K.J. Dickersn, T.C. Chiu, L.Y. Tsung, M.K. Jain, T.D. Bonifield, J.C. Ondrusek, and W.R. McKee, Proceedings of the IEEE 40th Annual International Reliability Physics Symposium (Dallas, TX, 2002), pp. 312–321.

M. Moriyama, S. Konishi, S. Tsukimoto, and M. Murakami, Mater. Trans. 45, 3172 (2004).

S. Konishi, M. Moriyama, and M. Murakami, Mater. Trans. 43, 1624 (2002).

A. Sekiguchi, J. Koike, S. Kamiya, M. Saka, and K. Maruyama, Appl. Phys. Lett. 79, 1264 (2001).

A. Hobbs, S. Murakami, T. Hosoda, S. Ohtsuka, M. Miyajima, S. Sugatani, and T. Makamura, Mater. Trans. 43, 1629 (2002).

T. Fujikawa, K. Suzuki, T. Masui, and T. Onishi, Advanced Metallization Conference, 1999, ed. M.E. Gross, T. Gessner, N. Kobayashi, and Y. Yasuda (Warrendale, PA: Materials Research Society, 1999), pp. 105–108.

K. Suzuki, T. Masui, T. Fujikawa, Y. Taguchi, and T. Kondo, Advanced Metallization Conference, 1999, ed. M.E. Gross, T. Gessner, N. Kobayashi, and Y. Yasuda (Warrendale, PA: Materials Research Society, 1999), pp. 155–160.

T. Fujikawa, T. Onishi, and T. Sato, Jpn. J. Appl. Phys. 40, 2191 (2001).

T. Onishi, H. Fujii, J. Munemasa, and T. Yoshikawa, Advanced Metallization Conference Asian Session 2001, ed. A.J. McKerrow, Y. Shacham-Diamond, S. Zaima, and T. Ohba (Warrendale, PA: Materials Research Society, 2001), pp. 245–250.

T. Onishi and T. Yoshikawa, Mater. Trans. 43, 1605 (2002).

T. Onishi, H. Fujii, T. Yoshikawa, J. Munemasa, T. Inoue, and A. Miyagaki, Thin Solid Films 425, 265 (2003).

P.G. Shewmon, Diffusion in Solids (New York: McGraw-Hill, 1963).

C. Herring, J. Appl. Phys. 21, 437 (1950).

A.C.F. Cooks, Appl. Solid Mech. 3, 30 (1989).

A.C.F. Cooks and A.A. Searle, Mech. Mater. 12, 279 (1991).

Acknowledgements

The authors wish to express their thanks to Professor T. Kitamura at Kyoto University for his useful advice and providing the calculation software for this work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Onishi, T., Mizuno, M., Yoshikawa, T. et al. Void Growth Behavior in ULSI Cu Interconnections by Grain-Boundary Diffusion Simulation. J. Electron. Mater. 39, 2255–2266 (2010). https://doi.org/10.1007/s11664-010-1311-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-010-1311-4