Abstract

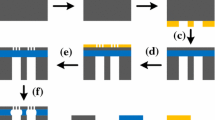

We observe hydrogen platelet buildup in single-crystalline silicon caused by hydrogen-plasma processing. The platelets are aligned along a layer of lattice defects formed in silicon before the plasma processing. The buried-defect layer is formed by either silicon-into-silicon or argon-into-silicon implantation. We discuss the platelet nucleation, growth, and merge phenomena and discuss applicability of the plasma hydrogenation to silicon-on-insulator (SOI) wafer fabrication by layer transfer.

Similar content being viewed by others

References

B. Aspar et al., J. Electron. Mater. 30, 834 (2001).

K. Henttinen, I. Suni, and S.S. Lau, Appl. Phys. Lett. 76, 2370 (2000).

Y. Zheng, S.S. Lau, T. Höchbauer, A. Misra, R. Verda, X.-M. He, M. Nastasi, and J.W. Mayer, J. Appl. Phys. 89, 2972 (2001).

T. Suni, A. Nurmela, I. Suni, S.S. Lau, T. Hochbauer, M. Nastasi, V.-M. Airaksinen, and K. Henttinen, Nucl. Instrum. Meth. B 190, 761 (2002).

W.N. Carr, B. Chen, A.Y. Usenko, and Y. Chabal, 2002 IEEE/SEMI Advanced Semiconductor Manufacturing Conf. Proc. (Piscataway, NJ: IEEE, 2002), pp. 6–10.

A. Agarwal, T.E. Haynes, V.C. Venezia, O.W. Holland, and D.J. Eaglesham, Appl. Phys. Lett. 72, 1086 (1998).

C. Qian, B. Terreault, and S.C. Gujrathi, Nucl. Instrum. Meth. B 175–177, 711 (2001).

Q.-Y. Tong, R. Scholz, U. Gösele, T.-H. Lee, L.-J. Huang, Y.-L. Chao, and T.Y. Tan, Appl. Phys. Lett. 72, 49 (1998).

A.Y. Usenko and W.N. Carr, in: Silicon-on-Insulator Technology and Devices X, ed. S. Cristoloveanu (Pennington, NJ: The Electrochemical Society, 2001), pp. 33–38.

A.Y. Usenko and W.N. Carr, Mater. Res. Soc. Symp. Proc. 681E, I3.3.1 (2001).

A.Y. Usenko and W.N. Carr, Proc. 2000 IEEE SOI Conf. (Piscataway, NJ: IEEE, 2000), pp. 16–17.

A.Y. Usenko, U.S. patent 6,368,938 (9 April 2002).

A.Y. Usenko, U.S. patent 6,352,909 (5 March 2002).

A.Y. Usenko and W.N. Carr, U.S. patent 6,346,459 (12 February 2002).

A.Y. Usenko, U.S. patent 6,344,417 (5 February 2002).

European Electronic Component Manufacturers Association and International SEMATECH, The International Technology Roadmap for Semiconductor (San Jose, CA: Semiconductor Industry Association, 2001), p. 7.

General specification for customized UNIBOND® Wafers, SOITEC, Parc technologique des Fontaines, 38190 Bernin, France, 2002.

C. Qian and B. Terreault, J. Appl. Phys. 90, 5152 (2001).

C. Qian and B. Terreault, Mater. Res. Soc. Symp. Proc. 585, 177 (2000).

C. Maleville, E. Neyret, E. Ecarnot, L. Arene, T. Barge, and A.J. Auberton, 2001 IEEE Int. SOI Conf. (Piscataway, NJ: IEEE, 2000), pp. 155–156.

K.V. Srikrishnan, U.S. patent 5,882,987 (16 March 1999).

V.P. Popov, I.V. Antonova, V.F. Stas, L.V. Mironova, A.K. Gutakovskii, E.V. Spesivtsev, A.S. Mardegzhov, A.A. Franznusov, and G.N. Feofanov, Mater. Sci. Eng. B-Solid B73, 82 (2000).

M.K. Weldon et al., J. Vac. Sci. Technol. B 15, 1065 (1997).

N.H. Nickel, G.B. Anderson, N.M. Johnson, and J. Walker, Phys. Rev. B 62, 8012 (2000).

N.M. Johnson, F.A. Ponce, R.A. Street, and R.J. Nemanich, Phys. Rev. B 35, 4166 (1987).

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Usenko, A. Layer-transfer process for silicon-on-insulator with improved manufacturability. J. Electron. Mater. 32, 872–876 (2003). https://doi.org/10.1007/s11664-003-0203-2

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/s11664-003-0203-2