Abstract

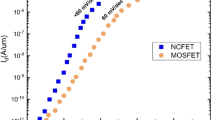

Various steep-slope devices based on novel structures and mechanisms garnered considerable attention for their potential in ultra-low power logic applications. In this work, a novel steep-slope negative quantum capacitance field-effect transistor (NQCFET) with molybdenum disulfide (MoS2)-integrated gate stack was realized by theoretical analysis and experimental evaluation. By combining the MoS2 equivalent capacitance model calibrated with experimental results, the NQCFET device model is further established. The results demonstrated that the optimized MoS2-integrated NQCFET can achieve a subthreshold swing (SS) of sub-60 mV/dec over a current range of 5 decades, with the minimum SS reaching 29 mV/dec, indicating the remarkable potential of MoS2-integrated NQCFETs for ultra-low power applications.

Similar content being viewed by others

References

Xu Q, Liu X, Wan B. In2O3 nanowire field-effect transistors with sub-60 mV/dec subthreshold swing stemming from negative capacitance and their logic applications. ACS Nano, 2018, 12: 9608–9616

Li X, Yuan P, Li L. Sub-5-nm monolayer GaSe MOSFET with ultralow subthreshold swing and high on-state current: dielectric layer effects. Phys Rev Appl, 2022, 18: 044012

Wang Y, Bai X, Chu J. Record-low subthreshold-swing negative-capacitance 2D field-effect transistors. Adv Mater, 2020, 32: 2005353

Ionescu A M, Riel H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature, 2011, 479: 329–337

Sarkar D, Xie X, Liu W. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature, 2015, 526: 91–95

Liang Z X, Zhao Y, Wang K F. Experimental investigation of a novel junction-modulated hetero-layer tunnel FET with the striped gate for low power applications. Sci China Inf Sci, 2023, 66: 169406

Salahuddin S, Datta S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett, 2008, 8: 405–410

Khan A I, Chatterjee K, Wang B. Negative capacitance in a ferroelectric capacitor. Nat Mater, 2015, 14: 182–186

Yang M X, Huang Q Q, Wang K F. Physical investigation of subthreshold swing degradation behavior in negative capacitance FET. Sci China Inf Sci, 2022, 65: 162404

Zhao Q T, Hartmann J M, Mantl S. An improved Si tunnel field effect transistor with a buried strained Si1−xGex Source. IEEE Electron Device Lett, 2011, 32: 1480–1482

Hraziia S, Vladimirescu A, Amara A. An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid-State Electron, 2012, 70: 67–72

Hoffmann M, Khan A I, Serrao C. Ferroelectric negative capacitance domain dynamics. J Appl Phys, 2018, 123: 184101

Obradovic B, Rakshit T, Hatcher R, et al. Ferroelectric switching delay as cause of negative capacitance and the implications to NCFETs. In: Proceedings of IEEE Symposium on VLSI Technology, Honolulu, 2018. 51–52

Li Y, Liang R, Wang J, et al. Negative capacitance oxide thin-film transistor with sub-60 mV/decade subthreshold swing. IEEE Electron Device Lett, 2019, 40: 826–829

Migita S, Ota H, Toriumi A, et al. Assessment of steep-subthreshold swing behaviors in ferroelectric-gate field-effect transistors caused by positive feedback of polarization reversal. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2018

Zhou J, Han G, Li Q, et al. Ferroelectric HfZrOx Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved IDS. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2016. 310–313

Zhou J, Peng Y, Han G, et al. Hysteresis reduction in negative capacitance Ge PFETs enabled by modulating ferroelectric properties in HfZrOx. IEEE J Electron Devices Soc, 2018, 6: 41–48

Kobayashi M. A perspective on steep-subthreshold-slope negative-capacitance field-effect transistor. Appl Phys Express, 2018, 11: 110101

Wang H, Yang M, Huang Q, et al. New insights into the physical origin of negative capacitance and hysteresis in NCFETs. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2018

Kopp T, Mannhart J. Calculation of the capacitances of conductors: Perspectives for the optimization of electronic devices. J Appl Phys, 2009, 106: 064504

He J, Hogan T, Mion T R. Spectroscopic evidence for negative electronic compressibility in a quasi-three-dimensional spin-orbit correlated metal. Nat Mater, 2015, 14: 577–582

Yang Y, Zhang K, Gu Y, et al. Steep-slope negative quantum capacitance field-effect transistor. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2022

Kumar V P, Panda D K. Review—next generation 2D material molybdenum disulfide (MoS2): properties, applications and challenges. ECS J Solid State Sci Technol, 2022, 11: 033012

Yang L, Majumdar K, Liu H. Chloride molecular doping technique on 2D materials: WS2 and MoS2. Nano Lett, 2014, 14: 6275–6280

Wang S T. On the I–V characteristics of floating-gate MOS transistors. IEEE Trans Electron Devices, 1979, 26: 1292–1294

Graham D W, Farquhar E, Degnan B, et al. Indirect programming of floating-gate transistors. IEEE Trans Circuits Syst I, 2007, 54: 951–963

Eisenstein J P, Pfeiffer L N, West K W. Negative compressibility of interacting two-dimensional electron and quasiparticle gases. Phys Rev Lett, 1992, 68: 674–677

Acknowledgements

This work was supported by National Key R&D Program of China (Grant No. 2018YFB2202801), National Natural Science Foundation of China (Grant No. 61927901), Beijing SAMT Project (Grant No. SAMT-BD-KT-22030101), 111 Project (Grant No. B18001), and Tencent Foundation through the Xplore Prize.

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Chen, L., Wang, H., Huang, Q. et al. A novel negative quantum capacitance field-effect transistor with molybdenum disulfide integrated gate stack and steep subthreshold swing for ultra-low power applications. Sci. China Inf. Sci. 66, 160406 (2023). https://doi.org/10.1007/s11432-023-3763-3

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11432-023-3763-3