Abstract

In this article, we comprehensively review recent progress in the ReRAM cell technology for 3D integration focusing on a material/device level. First we briefly mention pioneering work on high-density crossbar ReRAM arrays which paved the way to 3D integration. We discuss the two main proposed 3D integration schemes—3D horizontally stacked ReRAM vs 3D Vertical ReRAM and their respective advantages and disadvantages. We follow with the detailed memory cell design on important work in both areas, utilizing either filamentary or interface-limited switching mechanisms. We also discuss our own contributions on HfO2-based filamentary 3D Vertical ReRAM as well as TaO x /TiO2 bilayer-based self-rectifying 3D Vertical ReRAM. Finally, we summarize the present status and provide an outlook for the nearterm future.

Similar content being viewed by others

References

The digital universe of opportunities: rich data and the increasing value of the Internet of Things. http://www. emc.com/leadership/digital-universe/2014iview/executive-summary.htm

IBM. IBM details next generation of storage innovation. http://www-03.ibm.com/press/us/en/pressrelease/2020-9.wss

Burr G W, Kurdi B N, Scott J C, et al. Overview of candidate device technologies for storage-class memory. IBM J Res Dev, 2008, 52: 449–464

Burr G W, Shenoy R S, Virwani K, et al. Access devices for 3D crosspoint memory. J Vac Sci Technol B, 2014, 32: 040802

Hwang C S. Prospective of semiconductor memory devices: from memory system to materials. Adv Electron Mater, 2015, 1: 1400056

Kgil T, Roberts D, Mudge T. Improving NAND flash based disk caches. In: Proceedings of 35th International Symposium on Computer Architecture, Beijing, 2008. 327–338

Tanaka H, Kido M, Yahashi K, et al. Bit cost scalable technology with punch and plug processfor ultra high density flash memory. In: Proceedings of IEEE Symposium on VLSI Technology, Kyoto, 2007. 14–15

Nitayama A, Aochi H. Bit cost scalable (BiCS) technology for future ultra high density storage memories. In: Proceedings of IEEE Symposium on VLSI Technology, Kyoto, 2013. T61–T62

Park K T, Han J M, Kim D, et al. Three-dimensional 128Gb MLC vertical NAND flash-memory with 24-WL stacked layers and 50MB/s high-speed programming. In: Digest of Technical Papers of 2014 IEEE International Solid-State Circuits Conference, San Francisco, 2014. 334–335

Wang K L, Alzate J G, Amiri P K. Low-power non-volatile spintronic memory: STT-RAM and beyond. J Phys D Appl Phys, 2013, 46: 074003

Kim C, Kwon K, Park C, et al. A covalent-bonded cross-coupled current-mode sense amplifier for STT-MRAM with 1T1MTJ common source-line structure array. In: Digest of Technical Papers of 2015 IEEE International Solid-State Circuits Conference, San Francisco, 2015. 134–135

Noguchi H, Ikegami K, Kushida K, et al. A 3.3ns-access-time 71.2µW/MHz 1Mb embedded STT-MRAM using physically eliminated read-disturb scheme and normally-off memory architecture. In: Digest of Technical Papers of 2015 IEEE International Solid-State Circuits Conference, San Francisco, 2015. 136–137

Yamada J, Miwa T, Koike H, et al. A 128 kb FeRAM macro for a contact/contactless smart card microcontroller. In: Digest of Technical Papers of 2000 IEEE International Solid-State Circuits Conference, San Francisco, 2000. 270–271

Müller J, Büscke T S, Müller S, et al. Ferroelectric hafnium oxide: a CMOS-compatible and highly scalable approach to future ferroelectric memories. In: Proceedings of 2013 IEEE International Electron Devices Meeting, Washington DC, 2013. 280–283

Waser R, Aono M. Nanoionics-based resistive switching memories. Nat Mater, 2007, 6: 833–840

Govoreanu B, Kar G S, Chen Y Y, et al. 10 × 10 nm2 Hf/HfOx cross-bar resistive RAM with excellent performance, reliability and low-energy operation. In: Proceedings of 2011 IEEE International Electron Devices Meeting, Washington DC, 2011. 729–732

Wu M C, Lin Y W, Tseng T Y. Low-power and highly reliable multilevel operation in ZrO2 1T1R RRAM. Electron Dev Lett, 2011, 32: 1026–1028

Lee H Y, Chen P S, Wu T Y, et al. Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO2-based RRAM. In: Proceedings of 2008 IEEE International Electron Devices Meeting, San Francisco, 2008. 297–300

Lee M J, Lee C B, Lee D, et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5-x /TaO2-x bilayer structures. Nat Mater, 2010, 10: 625–630

Sawa A. Resistive switching in transition metal oxides, Mater Today, 2008, 11: 28–36

Waser R, Dittmann R, Staikov G, et al. Redox-based resistive switching memories—nanoionic mechanisms, prospects, and challenges. Adv Mat, 2009, 21: 2632–2663

Zhuge F, Li K, Fu B, et al. Mechanism for resistive switching in chalcogenide-based electrochemical metallization memory cells. AIP Adv, 2015, 5: 057125

Wedig A, Luebben M, Cho D Y, et al. Nanoscale cation motion in TaOx, HfOx and TiOx memristive systems. Nat Nanotechnol, 2016, 11: 67–74

Ahn S E, Lee M J, Park Y, et al. Write current reduction in transition metal oxide based resistance-change memory. Adv Mater, 2008, 20: 924–928

Kwon D H, Kim K M, Jang J H, et al. Atomic structure of conducting nanofilaments in TiO2 resistive switching memory. Nat Nanotech, 2010, 5: 148–153

Burr G W, Breitwisch M J, Franceschini M, et al. Phase change memory technology. J Vac Sci Technol B, 2010, 28: 223–262

Deringer V L, Dronskowski R, Wuttig M. Microscopic complexity in phase-change materials and its role for applications. Adv Funct Mat, 2015, 25: 6343–6359

Lam C H. Phase Change Memory and its intended applications. In: Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, 2014. 29.3.1–29.3.4

Stanisavljevic M, Athmanathan A, Papandreou N, et al. Phase-change memory: feasibility of reliable multilevelcell storage and retention at elevated temperatures. In: Proceedings of 2015 IEEE International Reliability Physics Symposium (IRPS), Monterey, 2015. 5B.6.1–5B.6.6

Edwards A H, Barnaby H J, Campbell K A, et al. Reconfigurable memristive device technologies. Proc IEEE, 2015, 103: 1004–1033

Lee J S, Lee S, Noh T W. Resistive switching phenomena: a review of statistical physics approaches. Appl Phys Rev, 2015, 2: 031303

Menzel S, Büttger U, Wimmer M, et al. Physics of the switching kinetics in resistive memories. Adv Funct Mat, 2015, 25: 6306–6325

Chen F T, Lee H Y, Chen Y S, et al. Resistance switching for RRAM applications. Sci China Inf Sci, 2011, 54: 1073–1086

Sheu S S, Chiang P C, Lin W P, et al. A 5 ns fast write multi-level non-volatile 1 Kbits RRAM memory with advance write scheme. In: Proceedings of 2009 Symposium on VLSI Circuits, Kyoto, 2009. 82–83

Wang C H, Tsai Y H, Lin K C, et al. Three-dimensional 4F2 ReRAM cell with CMOS logic compatible process. In: Proceedings of 2010 IEEE International Electron Devices Meeting, San Francisco, 2010. 664–667

Grossi A, Zambelli C, Olivo P, et al. Electrical characterization and modeling of pulse-based forming techniques in RRAM arrays. Solid-State Electron 2016, 115: 17–25

Linn E, Rosezin R, Kugeler C, Waser R. Complementary resistive switches for passive nanocrossbar memories. Nat Mater, 2010, 9: 403–406

Huang C H, Huang J S, Lin S M, et al. ZnO1-x nanorod arrays/ZnO thin film bilayer structure: from homojunction diode and high-performance memristor to complementary 1D1R application. ACS Nano, 2012, 6: 8407–8414

Huang J J, Tseng Y M, Hsu C W, et al. Bipolar nonlinear Ni/TiO2/Ni selector for 1S1R crossbar array applications. Electron Dev Lett, 2011, 32: 1427–1429

Deng Y X, Chen H Y, Gao B, et al. Design and optimization methodology for 3D RRAM arrays. In: Proceedings of 2013 IEEE International Electron Devices Meeting, Washington DC, 2013. 25.7.1–25.7.4

Tseng Y H, Huang C-E, Kuo C-H, et al. High density and ultra small cell size of Contact ReRAM (CR-RAM) in 90nm CMOS logic technology and circuits. In: Proceedings of 2009 IEEE International Electron Devices Meeting, Baltimore, 2009. 109–112

Sheu S-S, Chiang P-C, Lin W-P, et al. A 5ns fast write multi-level non-volatile 1 K bits RRAM memory with advance write scheme. In: Proceedings of 2009 Symposium on VLSI Circuits, Kyoto, 2009. 82–83

Wei Z, Kanzawa Y, Arita K, et al. Highly reliable TaOx ReRAM and direct evidence of redox reaction mechanism. In: Proceedings of 2008 IEEE International Electron Devices Meeting, San Francisco, 2008. 1–4

Wang X P, Fang Z, Li X, et al. Highly compact 1T-1R architecture (4F2 footprint) involving fully CMOS compatible vertical GAA nano-pillar transistors and oxide-based RRAM cells exhibiting excellent NVM properties and ultralow power operation. In: Proceedings of 2012 IEEE International Electron Devices Meeting, San Francisco, 2012. 20.6.1–20.6.4

Yasuhara R, Ninomiya T, Muraoka S, et al. Consideration of conductive filament for realization of low-current and highly-reliable TaOx ReRAM. In: Proceedings of 2013 5th IEEE International Memory Workshop (IMW), Monterey, 2013. 34–37

Zahurak J, Miyata K, Fischer M, et al. Process integration of a 27nm, 16Gb Cu ReRAM. In: Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, 2014. 140–143

Kau D C, Tang S, Karpov I V, et al. A stackable cross point phase change memory. In: Proceedings of 2009 IEEE International Electron Devices Meeting, Baltimore, 2009. 617–620

Tran X A, Gao B, Kang J F, et al. High performance unipolar AlOy/HfOx/Ni based RRAM compatible with Si diodes for 3D application. In: Proceedings of IEEE Symposium on VLSI Technology, Kyoto, 2011. 44–45

Kang M J, Park T J, Kwon YW, et al. PRAM cell technology and characterization in 20nm node size. In: Proceedings of 2011 IEEE International Electron Devices Meeting, Washington DC, 2011. 39–42

Choi Y, Song I, Park M-H, et al. A 20nm 1.8V 8Gb PRAM with 40MB/s program bandwidth. In: Digest of Technical Papers of 2012 IEEE International Solid-State Circuits Conference, San Francisco, 2012. 46–47

Lee M J, Park Y, Kang B S, et al. 2-stack 1D-1R coss-point structure with oxide diodes as switch elements for high density resistance RAM applications. In: Proceedings of 2007 IEEE International Electron Devices Meeting, Washington DC, 2007. 771–774

Lee M J, Seo S, Kim D C, et al. A low-temperature-grown oxide diode as a new switch element for high-density, nonvolatile memories. Adv Mater, 2007, 19: 73–76

Huang J J, Kuo C W, Chang W C, et al. Transition of stable rectification to resistive-switching in Ti/TiO2/Pt oxide diode. Appl Phys Lett, 2010, 96: 262901

Govoreanu B, Zhang L, Crotti D, et al. Thin-Silicon Injector (TSI): an all-silicon engineered barrier, highly nonlinear selector for high density resistive RAM applications. In: Proceedings of 2015 IEEE International Memory Workshop (IMW), Monterey, 2015. 1–4

Sasago Y, Kinoshita M, Morikawa T, et al. Cross-point phase change memory with 4F2 cell size driven by lowcontact-resistivity poly-Si diode. In: Proceedings of IEEE Symposium on VLSI Technology, Kyoto, 2009. 24–25

Cha E, Woo J, Lee D, et al. Selector devices for 3-D cross-point ReRAM. In: Proceedings of International Symposium on Circuits and Systems (ISCAS), Melbourne VIC, 2014. 428–431

Choi B J, Zhang J M, Norris K, et al. Trilayer tunnel selectors for memristor memory cells. Adv Mater, 2016, 28: 356–362

Kim G H, Lee J H, Ahn Y, et al. 32 × 32 crossbar array resistive memory composed of a stacked schottky diode and unipolar resistive memory. Adv Funct Mat, 2013, 23: 1440–1449

Huang J-J, Tseng Y-M, Luo W-C, et al. One selector-one resistor (1S1R) crossbar array for high-density flexible memory applications. In: Proceedings of 2011 IEEE International Electron Devices Meeting, Washington DC, 2011. 733–736

Kim S, Liu X, Park J, et al. Ultrathin (< 10 nm) Nb2O5/NbO2 hybrid memory with both memory and selector characteristics for high density 3D vertically stackable RRAM applications. In: Proceedings of IEEE Symposium on VLSI Technology, Honolulu, 2012. 155–156

Lee H D, Kim S G, Cho K, et al. Integration of 4F2 selector-less crossbar array 2Mb ReRAM based on transition metal oxides for high density memory applications. In: Proceedings of IEEE Symposium on VLSI Technology, Honolulu, 2012. 151–152

Kim W G, Lee H M, Kim B Y, et al. NbO2-based low power and cost effective 1S1R switching for high density cross point ReRAM application. In: Proceedings of IEEE Symposium on VLSI Technology, Honolulu, 2014. 1–2

Lee S, Lee D, Woo J, et al. Selector-less ReRAM with an excellent non-linearity and reliability by the band-gap engineered multi-layer titanium oxide and triangular shaped AC pulse. In: Proceedings of 2013 IEEE International Electron Devices Meeting, Washington DC, 2013. 272–275

Jo S H, Kumar T, Narayanan S, et al. 3D-stackable crossbar resistive memory based on field assisted superlinear threshold (FAST) selector. In: Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, 2014. 160–163

Seok J Y, Song S J, Yoon J H, et al. A review of three-dimensional resistive switching cross-bar array memories from the integration and materials property points of view. Adv Funct Mat, 2014, 24: 5316–5339

Baek I G, Park C J, Ju H, et al. Realization of vertical resistive memory (VRRAM) using cost effective 3D process. In: Proceedings of 2011 IEEE International Electron Devices Meeting (IEDM), Washington DC, 2011. 31.8.1–31.8.4

Yoon H S, Baek I-G, Zhao J, et al. Vertical cross-point resistance change memory for ultra-high density non-volatile memory applications. In: Proceedings of IEEE Symposium on VLSI Technology, Kyoto, 2009. 26–27

Zhang L Q, Cosemans S, Wouters D J, et al. Analysis of vertical cross-point resistive memory (VRRAM) for 3D RRAM design. In: Proceedings of 2013 5th IEEE International Memory Workshop, Monterey, 2013. 155–158

Xu C, Niu D, Yu S, Xie Y. Modeling and design analysis of 3D vertical resistive memory—a low cost cross-point architecture. In: Proceedings of 19th Asia and South Pacific Design Automation Conference (ASP-DAC), Singapore, 2014. 825–830

Chevallier C J, Siau C H, Lim S F, et al. A 0.13µm 64Mb multi-layered conductive metal-oxide memory. In: Digest of Technical Papers of 2010 IEEE International Solid-State Circuits Conference, San Francisco, 2010. 260–261

Meyer R, Schloss L, Brewer J, et al. Oxide dual-layer memory element for scalable non-volatile cross-point memory technology. In: Proceedings of 9th Annual Non-Volatile Memory Technology Symposium (NVMT), Pacific Grove, 2008. 1–5

Kawahara A, Azuma R, Ikeda Y, et al. An 8Mb multi-layered cross-point ReRAM macro with 443MB/s write throughput. In: Proceedings of 2012 IEEE International Solid-State Circuits Conference, San Francisco, 2012. 432–434

Liu T-Z, Yan T H, Scheuerlein R, et al. A 130.7mm2 2-layer 32Gb ReRAM memory device in 24nm technology. In: Digest of Technical Papers of 2013 IEEE International Solid-State Circuits Conference, San Francisco, 2013. 210–211

Intel and Micron Produce Breakthrough Memory Technology. http://newsroom.intel.com/community/intelnewsroom/blog/2015/07/28/intel-and-micron-produce-breakthrough-memory-technology

Chin Y-W, Chen S-E, Hsieh M-C, et al. Point twin-bit RRAM in 3D interweaved cross-point array by Cu BEOL process. In: Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, 2014. 148–151

Chien W C, Lee F M, Lin Y Y, et al. Multi-layer sidewall WOX resistive memory suitable for 3D ReRAM. In: Proceedings of 2012 Symposium on VLSI Technology (VLSIT), Honolulu, 2012. 153–154

Chen H-Y, Yu S M, Gao B, et al. HfOx based vertical resistive random access memory for cost-effective 3D crosspoint architecture without cell selector. In: Proceedings of 2012 IEEE International Electron Devices Meeting, San Francisco, 2012. 497–500

Yu S M, Chen H-Y, Gao B, et al. HfOx-based vertical resistive switching random access memory suitable for bitcost-effective three-dimensional cross-point architecture. ACS Nano, 2013, 7: 2320–2325

Yu S M, Chen H-Y, Deng Y, et al. 3D Vertical RRAM—scaling limit analysis and demonstration of 3D array operation. In: Proceedings of IEEE Symposium on VLSI Technology, Kyoto, 2013. T158–T159

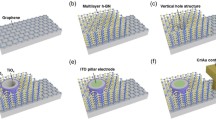

Sohn J, Lee S, Jiang Z, et al. Atomically thin graphene plane electrode for 3D RRAM. In: Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, 2014. 116–119

Zhao L, Jiang Z, Chen H-Y, et al. Ultrathin (~ 2 nm) HfOx as the fundamental resistive switching element: thickness scaling limit, stack engineering and 3D Integration. In: Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, 2014. 156–159

Gao B, Chen B, Liu R, et al. 3-D cross-point array operation on AlOy/HfOx-based vertical resistive switching memory. IEEE Trans Electron Dev, 2014, 61: 1377–1381

Bai Y, Wu H Q, Wu R, et al. Study of multi-level characteristics for 3D vertical resistive switching memory. Sci Rep, 2014, 4: 5780

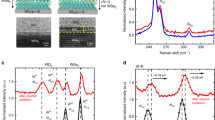

Hudec B, Wang I-T, Lai W-L, et al. Interface engineered HfO2-based 3D vertical ReRAM. J Phys D Appl Phys, 2016, 49: 215102

Jancovic B, Hudec B, Dobrocka E, et al. Resistive switching in HfO2-based atomic layer deposition grown metalinsulator-metal structures. Appl Surf Sci, 2014. 312: 112–116

Butcher B, Bersuker G, Young-Fischer K G, et al. Hot forming to improve memory window and uniformity of low-power HfOx based RRAMs. In: Proceedings of 2012 4th IEEE International Memory Workshop, Milan, 2012. 1–4

Kalantarian A, Bersuker G, Gilmer D C, et al. Controlling uniformity of RRAM characteristics through the forming process. In: Proceedings of 2012 IEEE International Reliability Physics Symposium (IRPS), Anaheim, 2012. 6C.4.1–6C.4.5

Walczyk D, Walczyk Ch, Schroeder T, et al. Resistive switching characteristics of CMOS embedded HfO2-based 1T1R cells. Microelectron Eng, 2011, 88: 1133–1135

Yang J J, Zhang M-X, Pickett M D, et al. Engineering nonlinearity into memristors for passive crossbar applications. Appl Phys Lett, 2012, 100: 113501

Park S-G, Yang M K, Ju H, et al. A non-linear ReRAM cell with sub-1µA ultralow operating current for high density vertical resistive memory (VRRAM). In: Proceedings of 2012 IEEE International Electron Devices Meeting, San Francisco, 2012. 501–504

Govoreanu B, Redolfi A, Zhang L, et al. Vacancy-modulated conductive oxide resistive ram (VCMO-RRAM): an area-scalable switching current, self-compliant, highly nonlinear and wide on/off-window resistive switching cell. In: Proceedings of 2013 IEEE International Electron Devices Meeting, Washington DC, 2013. 256–259

Chen Y-S, Lee H-Y, Chen P-S, et al. Novel defects-trapping TaOx/HfOx RRAM with reliable self-compliance, high nonlinearity, and ultra-low current. IEEE Electron Dev Lett, 2014, 35: 202–204

Yoon J H, Kim K M, Song S J, et al. Pt/Ta2O5/HfO2-x /Ti resistive switching memory competing with multilevel NAND flash. Adv Mater, 2015, 27: 3811–3816

Yoon J H, Song S J, Yoo I-H, et al. Highly uniform, electroforming-free, and self-rectifying resistive memory in the Pt/Ta2O5/HfO2-x /TiN structure. Adv Funct Mater, 2014, 24: 5086–5095

Hsu C-W, Wang I-T, Lo C-L, et al. Self-rectifying bipolar TaOx/TiO2 RRAM with superior endurance over 1012 cycles for 3D high-density storage-class memory. In: Proceedings of IEEE Symposium on VLSI Technology, Kyoto, 2013. T166–T167

Hsu C-W, Wan C-C, Wang I-T, et al. 3D vertical TaOx/TiO2 RRAM with over 103 self-rectifying ratio and sub-µA operating current. In: Proceedings of 2013 IEEE International Electron Devices Meeting, Washington DC, 2013. 10.4.1–10.4.4

Hsu C-W, Wang Y-F, Wan C-C, et al. Homogeneous barrier modulation of TaOx/TiO2 bilayers for ultra-high endurance three-dimensional storage-class memory. Nanotechnology, 2014, 25: 165202

Wang Y-F, Lin Y-C, Wang I-T, et al. Characterization and modeling of nonfilamentary Ta/TaOx/TiO2/Ti Analog Synaptic Device. Sci Rep, 2015, 5: 10150

Lai W-L, Chou C-T, Hsu C-W, et al. Interface engineering in homogeneous barrier modulation RRAM for 3D vertical memory applications. In: Proceedings of International Conference on Solid State Devices and Materials, Tsukuba, 2014. 412–413

Chou C-T, Hudec B, Hsu C-W, et al. Crossbar array of selector-less TaOx/TiO2 bilayer RRAM. Microelectron Reliab, 2015, 55: 2220–2223

Kim S, Du C, Sheridan P, et al. Experimental demonstration of a second-order memristor and its ability to biorealistically implement synaptic plasticity. Nano Lett, 2015, 15: 2203–2211

Burr G W, Shelby R M, Sidler S, et al. Experimental demonstration and tolerancing of a large-scale neural network (165000 synapses) using phase-change memory as the synaptic weight element. IEEE Trans Electron Dev, 2015, 62: 3498–3507

Wang I-T, Lin Y-C, Wang Y-F, et al. 3D synaptic architecture with ultralow sub-10 fJ energy per spike for neuromorphic computation. In: Proceedings of 2014 IEEE International Electron Devices Meeting, San Francisco, 2014. 28.5.1–28.5.4

Gao B, Wang I-T, Chen P-Y, et al. Fully parallel write/read in resistive synaptic array for accelerating on-chip learning. Nanotechnology, 2015, 26: 455204

Siemon A, Breuer T, Aslam N, et al. Realization of boolean logic functionality using redox-based memristive devices. Adv Funct Mater, 2015, 25: 6414–6423

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Hudec, B., Hsu, CW., Wang, IT. et al. 3D resistive RAM cell design for high-density storage class memory—a review. Sci. China Inf. Sci. 59, 061403 (2016). https://doi.org/10.1007/s11432-016-5566-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11432-016-5566-0