Abstract

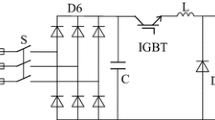

This paper presents a single event transient (SET) suppressor circuit, which can suppress the effect of SET in charge pump (CP) on the whole PLL frequency synthesizers, and at the same time it brings little negative effect to the system during normal operation. Because the proposed SET suppressor circuit only includes a resistor, a PMOS and an NMOS device, little area penalty is introduced. By preventing SET propagating from CP to low pass filter (LPF) and VCO when a single event strikes on CP output node, the system shows excellent hardness to SET in CP. Mixed simulations are performed on TCAD workbench. The results show that a single event with an LET at 80 MeV cm2/mg can only induce approximately 2.3 mV disturbance on the control voltage of VCO.

Similar content being viewed by others

References

Boulghassoul Y, Massengill L W, Sternberg A L, et al. Towards SET mitigation in RF digital PLLs: From error characterization to radiation hardening considerations. IEEE Trans Nucl Sci, 2006, 53: 2047–2053

Loveless T D, Massengill L W, Bhuva B L, et al. A hardened-by-design technique for RF digital phase-locked loops. IEEE Trans Nucl Sci, 2006, 53: 3432–3438

Loveless T D, Massengill L W, Bhuva B L, et al. A single-event-hardened phase-locked loops. IEEE Trans Nucl Sci, 2007, 54: 2012–2020

Daniel T, Massengill L W, Bhuva B L, et al. A probabilistic analysis technique applied to a radiation-hardened-by-design voltagecontrolled oscillator for mixed-signal phase-locked loops. IEEE Trans Nucl Sci, 2008, 55: 3447–3455

Zhao Z Y, Li J F, Chen S M, et al. A radiation-hardened-by-design technique for improving single-event transient tolerance of charge pumps in PLLs. J Semicond, 2009, 30(12): 125009

Kauppila J S, Sternberg A L, Alles M L, et al. A bias-dependent single-event compact model implemented into BISM4 and a 90 nm CMOS process design kit. IEEE Trans Nucl Sci, 2009, 56: 3152–3157

Gupta S D, Witulski A F, Bhuva B L, et al. Effect of well and substrate potential modulation on single event pulse shape in deep submicro CMOS. IEEE Trans Nucl Sci, 2007, 54: 2407–2412

Turowski M, Raman A, Jablonski G. Mixed-mode simulation and analysis of digital single event transients in fast CMOS ICs. In: Proc 14th Int Conf MIXDES, 2007. 443–439

Amusan O, Witulski A F, Massengill L W, et al. Charge collection and charge sharing in a 130 nm CMOS technolog. IEEE Trans Nucl Sci, 2006, 53: 3253–3258

Amusan O, Massengill L W, Baze M P, et al. Migtigation techniques for single event induced charge sharing in a 90 nm bulk CMOS process. In: Proc 46th IEEE IRPS, 2008. New York: IEEE, 2008. 486–472

Chung H H, Chen W J, Bakkaloglu B, et al. Analysis of single events effects on monolithic PLL frequency synthesizers. IEEE Trans Nucl Sci, 2006, 53: 3539–3543

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Han, B., Guo, Z., Wang, X. et al. A radiation-hardened-by-design technique for suppressing SET in charge pump of PLL frequency synthesizer. Sci. China Technol. Sci. 56, 286–292 (2013). https://doi.org/10.1007/s11431-012-5086-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11431-012-5086-0