Abstract

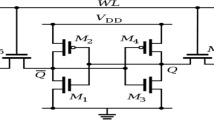

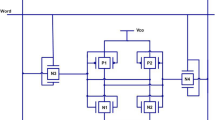

As the technology is scaled the power consumption increases significantly, because of which the battery life of portable devices is reduced. Due to high power density, the increased power consumption becomes an obstacle for scaling of devices. Power optimization is the most significantly visible in future portable IC’s. As per increasing need for a low power circuit, the reduction in leakage current becomes very important aspect while designing any IC. The leakage can be reduced by altering the threshold voltage. Further as the technology is scaled FinFET is the alternate for CMOS with increased control of gate over the channel. In this paper a FinFET based 7T SRAM cell is proposed which is faster in its operation and consumes less power. In order to further reduce the leakage power, FinFET based 7T SRAM cell is designed using self-controllable voltage level (SVL) techniques. In this paper, an 18 nm FinFET based SRAM cell is designed using SVL circuit to reduce the leakage current and power. The proposed design has the least leakage current of 16.56 nA and leakage power of 11.59 nW by using the combined technique of LSVL and USVL. All the circuit design and simulation have been done in Cadence Virtuoso using 18 nM FinFET technology.

Similar content being viewed by others

References

Bowman, K. A., Duvall, S. G., & Meindl, J. D. (2002). Impact of die-to-die and within-die parameter fluctuations on the maximum clock frequency distribution for gigascale integration. IEEE Journal of Solid-State Circuits, 37(2), 183.

kumar, T. S., & Tripathi, S. L. (2019). Implementation of CMOS SRAM Cells in 7, 8, 10 and 12-transistor topologies and their performance comparison. International Journal of Engineering and Advanced Technology, 8(2S2), 227–229.

Rathod, S. S., Saxena, A. K., & Dasgupta, S. (2010). A proposed DG-FinFET based SRAM cell design with RadHard capabilities. Microelectronics Reliability, 50(8), 1039–1190.

Kushwah, C. B., Vishvakarma, S. K., & Dwivedi, D. (2016). A 20nm robust single-ended boostless 7T FinFET sub-threshold SRAM cell under process–voltage–temperature variation. Microelectronics Journal, 51, 75–88.

Sil, A., Bakkamanthala, S., karlapudi, S., & Bayoumi, M. (2012). Highly Stable, Dual-port, Sub-threshold 7T SRAM Cell for Ultra-low Power Application. In IEEE International NEWCAS Conference (pp. 493–496).

Ansari, M., Afzali-Kusha, H., Ebrahimi, B., Navabi, Z., Afzali-Kushaa, A., & Pedram, M. (2015). A near-threshold 7T SRAM cell with high write and read margins and low write time for sub-20 nm FinFET technologies. Integration the VLSI Journal, 50, 91–106.

kumar, V., Mahor, V., pattanaik, M. (2016). Novel Ultra Low Leakage FinFET Based SRAM Cell. In IEEE International Symposium on Nanoelectronic and Information Systems (pp. 89–92).

Endo, K., Shin-Ichioinchi, Ishikawa, Y., Liu, Y., Matsukawa, T., Sakamoto, K., Masahara, M., Tsukada, J., Ishii, K., Yamauchi, H., & Suzuki, E., (2009) Independent-Double-Gate FinFET SRAM for leakage current reduction. IEEE Electron Device letters, 30(7), 757–759.

Tripathi, S.L., Mishra, R., Narendra, V., & Mishra, R.A. (2013) High performance Bulk FinFET with Bottom Spacer. In IEEE CONECCT (pp.1–5).

Gavaskar, K., & Ragupathy, U. S. (2019). Low power self-controllable voltage level and low swing logic based 11T SRAM cell for high speed CMOS circuits. Analog Integrated Circuits and Signal Processing, 100(1), 61–77.

Satish, M. N., Vasundara Patel K. S. (2019). Power Reduction in FinFET Half Adder using SVL Technique in 32 nm Technology. In IEEE MEC International Conference on Big Data and Smart City (ICBDSC)

Birla, S., Shukla, N. K., Pattanaik, M., & Singh, R. K. (2010). Device-and-circuit-design-challenges-for-low-leakage-SRAM for ultra low power applications. Canadian Journal on Electrical & Electronics Engineering, 1(7), 156–167.

Gupta, D. C., & Raman, A. (2012). Analysis of leakage current reduction techniques in SRAM cell in 90 nm CMOS technology. IJCA, 50(19), 18–22.

Duari, C., & Birla, S. (2018). Leakage power improvement in SRAM cell with clamping diode using reverse body bias technique. In International Conference on Data Engineering and Communication Technology, Advances in Intelligent Systems and Computing (Vol. 828). Springer.

Manorama, Khandelwal, S., Akashe, S. (2013). Design of a FinFET based inverter using MTCMOS and SVL leakage reduction technique. In: Students Conference on Engineering and Systems (SCES) (pp. 12–14)

Akashe, S., & Sharma, S. (2013). Leakage current reduction techniques for 7T SRAM cell in 45 nm technology. Wireless Personal Communication, 71, 123–136.

Enomoto, T., Oka, Y., & Shikano, H. (2003). Self-controllable voltage level (SVL) circuit and its low-power high-speed CMOS circuit applications. IEEE Journal of Solid State Circuits, 38(7), 1220–1226.

Akashe, S., Mishra, M., & Sharma, S. (2012). Self-controllable voltage level circuit for low power, high speed 7T SRAM cell at 45 nm technology. In IEEE Conference on Engineering and Systems (pp. 1–5).

Kumar N. S., Sudhanva N. G., Hande V. S., Sajjan M. V., Kumar C. S. H., Kariyappa B. S., SRAM design using memristor and self-controllable voltage (SVL) technique. In International Conference on Computational Intelligence and Data Engineering. Lecture Notes on Data Engineering and Communications Technologies, Springer, Vol. 9, pp. 29–39.

Akashe, S., & Shrivas, J. (2013). Optimization of leakage current and leakage power of full adder by using self-controlled voltage level technique in nanometer regime. Quantum Matter, 2(2), 137–139.

Mohanty, S., Singh, J., Kougians, E., & Pradhan, D. (2012). Statistical DOE-ILP based power-performance-process (P3) optimization of nano- CMOS SRAM INTIGRATION. The VLSI Journal, 45, 33–45.

Triapthi, S. L., (2019). Low Power High Performance Tunnel FET, Analysis for IoT applications. IGI global publisher, PP. 47–57. https://doi.org/10.4018/978-1-5225-9574-8.ch002.

Guo X., & Stan M. R. (2020) Design and aging challenges in FinFET circuits and internet of things (IoT) applications. In: Circadian rhythms for future resilient electronic systems. Springer, Cham, 2019, pp. 143–189. https://doi.org/10.1007/978-3-030-20051-0_6.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, T.S., Tripathi, S.L. Leakage Reduction in 18 nm FinFET based 7T SRAM Cell using Self Controllable Voltage Level Technique. Wireless Pers Commun 116, 1837–1847 (2021). https://doi.org/10.1007/s11277-020-07765-6

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-020-07765-6