Abstract

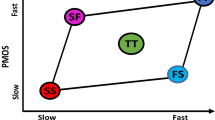

The aggressive scaling of CMOS technology has inevitably led to vastly increased power dissipation, process variability and reliability degradation, posing tremendous challenges to robust circuit design. To continue the success of integrated circuits, advanced design research must start in parallel with or even ahead of technology development. In this paper, an attempt is made to analyze various circuits’ delay and power performance by introducing certain level of variation to important process parameters like threshold voltage (Vth), mobility of carriers (μ0), oxide thickness (tox) and doping concentration (nsd). Basic Monte Carlo simulation is carried out on these circuits to ascertain the stability in performances. A 16 × 1 multiplexer is considered for detailed analysis. SPICE characterization is done for three different input slew rates (0.1, 0.5 and 1 ns) against four different output load drive strengths (1×, 2×, 3× and 4× output capacitive load). From the obtained results, output slew rates and average power results are observed and discussed.

Similar content being viewed by others

References

Wong, B. P., Mittal, A., Cao, Y., & Starr, G. (2005). Nano-CMOS circuit and physical design. New York: Wiley Interscience.

Kim, Y.-B. (2010). Challenges for nanoscale MOSFETs and emerging nanoelectronics. Transactions on Electrical And Electronic Materials, 11(3), 93–105.

Taur, Y. (2002). CMOS design near the limit of scaling. IBM Journal of Research and Development, 46(2/3), 213–222.

Lin, L., & Burleson, W. (2009). Analysis and mitigation of process variation impacts on power-attack tolerance. In Proceedings of the 46th annual design automation conference (pp. 238–243).

International Technology Roadmap for Semiconductors (ITRS). (2011). http://www.itrs.org.

Vaddi, R., Dasgupta, S., & Agarwal, R. P. (2010). Device and circuit co-design robustness studies in the subthreshold logic for ultralow-power applications for 32 nm CMOS. IEEE Transactions on Electron Devices, 57(3), 654–664.

Srivatsava, A., Kachru, T., & Sylvester, D. (2007). Low-power-design space exploration considering process variation using robust optimization. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 26(1), 67–79.

Schulz, T., Pacha, C., Luyken, R. J., Städele, M., Hartwich, J., Dreeskornfeld, L., et al. (2004). Impact of technology parameters on device performance of UTB-SOI CMOS. Solid-State Electronics, 48(4), 521–527.

Berkeley Predictive Technology Model, University of California, Berkeley. (2004). (http://www.device.eecs.berkeley.edu/~ptm/).

Zhao, W., & Cao, Y. (2006). New generation of predictive technology model for sub-45 nm early design exploration. IEEE Transactions on Electron Devices, 53(11), 2816–2823.

Cao, Y., Balijepalli, A., Sinha, S., Wang, C.-C., Wang, W., & Zhao, W. (2009). The predictive technology model in the late silicon era and beyond. Foundations and Trends in Electronic Design Automation, 3(4), 305–401.

Yu, B., Wang, H., Riccobene, C., Xiang, Q., & Lin, M. R. (2000). Limits of gate-oxide scaling in nano-transistors (pp. 90–91). Honolulu: IEEE Symposium on VLSI Technology.

Sirisantana, N., Wei, L., & Roy, K. (2000). High-performance low-power CMOS circuits using multiple channel length and multiple oxide thickness. In Proceedings of international conference on computer design (pp. 227–232).

BSIM4.3.0 MOSFET Model—User’s manual. (2003). http://www-device.eecs.berkeley.edu/bsim3/~bsim4.html.

Bhattacharyya, A. B. (2009). Compact MOSFET models for VLSI design. New York: Wiley.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Udaiyakumar, R., Joseph, S., Sundararajan, T.V.P. et al. Performance Analysis in Digital Circuits for Process Corner Variations, Slew-Rate and Load Capacitance. Wireless Pers Commun 103, 99–115 (2018). https://doi.org/10.1007/s11277-018-5428-8

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-018-5428-8