Abstract

Emerging standards for wireless communications in the 60-GHz band, such as WiGig and IEEE 802.11ad, require high throughput between 1.5 and 6 Gb/s. These standards use adaptive low-density parity-check (LDPC) codes for high error correction capability. Most research studies on LDPC decoders have focused on low area implementations, to improve throughput. We previously developed a bit-serial first two minimum-value generator without bit error rate (BER) performance degradation. This paper presents a low-complexity bit-wise LDPC decoder based on bit-serial first two minimum-value generator for a high-data-rate LDPC decoder. We use the throughput-to-area ratio (TAR) metric to compare with other 802.11ad LDPC decoders.

Similar content being viewed by others

References

Gallager, R. G. (1963). Low-density parity-check codes. Cambridge: MIT Press.

MacKay, D. J. C., Neal, R. M. Good codes based on very sparse matrices, in Cryptography and Coding. 5th IMA Conference (Lecture Notes in Computer Science), C.

Richardson, T. J., & Urbanke, R. L. (2001). The capacity of low-density parity check codes under message-passing decoding. IEEE Transactions on Information Theory, 47(2), 599–618.

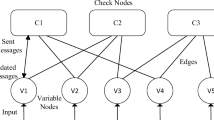

Kschischang, F., Frey, B., & Loeliger, H.-A. (2001). Factor graphs and the sum-product algorithm. IEEE Transactions on Information Theory, 47(2), 498–519.

Fossorier, M. P. C., Mihaljević, M., & Imai, H. (1999). Reduced complexity iterative decoding of low-density parity check codes based on belief propagation. IEEE Transactions on Communications, 47(5), 673–680.

Chen, J., Dholakia, A., Eleftheriou, E., Fossorier, M.P.C., and Hu, X.-Y. (2005) Reduced-complexity decoding of LDPC codes,” IEEE Trans. Commun., vol. 53.

Hemati, S., Leduc-Primeau, F., & Gross, W. J. (2016). A relaxed min-sum LDPC decoder with simplified check nodes. IEEE Communications Letters, 20(3), 422–425.

IEEE 802.11n. (2006) Wireless LAN Medium Access Control and Physical Layer specifications: Enhancements for Higher Throughput. IEEE P802.16n/D1.0.

“ISO/IEC/IEEE International Standard for Information technology Telecommunications and information exchange between systems—Local and metropolitan area networks—Specific requirements-Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications Amendment 3: Enhancements for Very High Throughput in the 60 GHz Band (adoption of IEEE Std 802.11ad-2012),” in ISO/IEC/IEEE 8802–11:2012/Amd.3:2014(E), ed, 2014, pp.1–634.

IEEE P802.3an, 10GBASE-T task force. http://www.ieee802.org/3/an.

IEEE Standard for Information Technology-Telecommunications and Information Exchange between Systems-Local and Metropolitan Area Networks-Specific Requirements-Part 11 (2012): Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications Amendment 3: Enhancements for Very High Throughput in the 60 GHz Band IEEE Std. 802.11ad.

IEEE draft standard for information technology-wireless LANs-part 21: mmWave PHY specification, (2010), IEEE Std. 802.11ad.

Ajaz, S., & Lee, H. (Sep. 2013). Reduced-complexity local switch based multi-mode QC-LDPC decoder architecture for Gbit wireless communication. Electronics Letters, 49(19), 1246–1248.

Balatsoukas-Stimming, A., Preyss, N., Cevrero, A., Burg, A., Roth, C. (2013) A parallelized layered QC-LDPC decoder for IEEE 802.11ad, New Circuits and Systems Conference (NEWCAS).

Li, M., Naessens, F., Li, M., Debacker, P., Desset, C., Raghavan P., Dejonghe, A., and Van der Perre, L. (2013) A processor based multi-standard low-power LDPC engine for multi-Gbps wireless communication, in IEEE Global Conference on Signal and Information Processing (GlobalSIP), pp. 1254–1257.

Li, M., Lee, Y., Huang, Y., & Perre, L. V. d. (2015). Area and energy efficient 802.11ad LDPC decoding processor. IET Electronics Letters, 51, 339–341.

Park, Y. S., Blaauw, D., Sylvester, D., & Zhang, Z. (2014). Low-power high-throughput LDPC decoder using non-refresh embedded DRAM. IEEE Journal of Solid-State Circuits, 49, 783–794.

Wey, C., Shieh, M., & Lin, S. (Dec. 2008). Algorithms of finding the first two minimum values and their hardware implementation. IEEE Trans. Circuits Syst. I, Reg. Papers, 55(11), 3430–3437.

Weiner, M., Nikoli, B., and Zhang, Z. (2011) LDPC decoder architecture for high-data rate personal-area networks, in Circuits and Systems (ISCAS), 2011 IEEE International Symposium on, pp. 1784–1787.

Amaru, L., Martina, M., & Masera, G. (2012). High speed architectures for finding the first two maximum/minimum values. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 20(12), 2342–2346.

Ho, K., Chen, C., & Chang, H. (2016). A 520k (18900, 17010) array dispersion LDPC decoder architectures for NAND flash memory. IEEE Trans. VLSI Systems, 24(4), 1293–1304.

Darabiha, A., Carusone, A. C., & Kschischang, F. R. (2008). Power reduction techniques for LDPC decoders. IEEE Journal of Solid-State Circuits, 43(8), 1835–1845.

Lee, J. H, Sunwoo, M. H (2016) Low-Complexity First-Two-Minimum-Values Generator for Bit-Serial LDPC Decoding, IEEE Transactions on Circuits and Systems-II.

Angarita, F., Sansaloni, T., Canet, M. J., & Valls, J. (2012). Improved sliced message passing architecture for high Thoughput decoding of LDPC codes. Journal of Signal Processing Systems, 66, 99–104.

Anastasopoulos, A. (2001) A comparison between the sum-product and the min-sum iterative detection algorithms based on density evolution, in Proc. IEEE Globecom, San Antonio, TX, pp. 1021–1025.

Kumawat, S., Shrestha, R., Daga, N., & Paily, R. (2015). High-throughput LDPC-decoder architecture using efficient comparison techniques dynamic multi-frame processing schedule. IEEE Transactions on circuits and systems—I: regular papaers, 62(5), 1421–1430.

Weiner, M. G, et al (2014) A Scalable 1.5 to 6Gb/s, 6.2 to 38.1mW LDPC decoder for 60GHz wireless networks in 28nm UTBB FDSOI, IEEE Int’l Solid-State Circuits Conf, ISSCC’14, San Francisco, CA, to appear.

Baccarani, G., Wordeman, M. R., & Dennard, R. H. (1984). Generalized scaling theory and its application to 1/4 micrometer MOSFET design. IEEE Transactions on Electron Devices, 31, 452–462.

Marshall, P. A., Gaudet, V. C., & Elliott, D. G. (2012). Deeply pipelined digitserial LDPC decoding. IEEE Trans. Circuits Syst. I, Reg. Papers, 59(12), 2934–2944.

Acknowledgments

This research was supported by the MSIT(Ministry of Science and ICT), Korea, under the ITRC(Information Technology Research Center) support program(IITP-2018-2016-0-00309-002) supervised by the IITP(Institute for Information & communications Technology Promotion) by the National Research Foundation of Korea by the Korea government (NRF-2017R1A2A2A05001046).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Lee, J.H., Sunwoo, M.H. Low-Complexity High-Throughput Bit-Wise LDPC Decoder. J Sign Process Syst 91, 855–862 (2019). https://doi.org/10.1007/s11265-018-1398-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-018-1398-z