Abstract

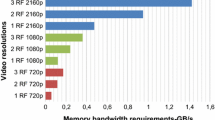

This paper presents a real-time, rate controlled, end-to-end (encoder and decoder) hardware solution for memory compression of raster-order video streams—named RImCom (short for Raster-order Image Compression). RImCom offers up to 3x compression that is either lossless or lossy at very reasonable PSNR values. The 180 nm ASIC implementation of RImCom achieves 28 fps at Ultra-HD resolution in the slow corner of synthesis. RImCom can match the fps of the state-of-the-art in the literature with 20 % less area or can achieve twice the fps with 55 % more area. Our FPGA implementation is the only end-to-end FPGA solution in the literature to achieve to this day over 60 fps at Full-HD resolution and to offer rate control. This work was motivated by video processing applications that require the previous frame(s) besides the current frame. When processing HD video streams, even when only one previous frame is required besides the current frame, a significant size and bandwidth of memory is needed. If the current frame is compressed on-the-fly with RImCom or a similar solution and stored on DRAM, and the previous frame is read from DRAM and decompressed with a small IP block, then the overall system cost, power consumption, and electromagnetic radiation are reduced.

Similar content being viewed by others

References

Micron system power calculator. https://www.micron.com/support/tools-and-utilities/power-calc.

Xiph.org test media collection. https://media.xiph.org/video/derf/.

Chen, W.Y., Ding, L.F., Tsung, P.K., & Chen, L.G. (2008). Architecture design of high performance embedded compression for high definition video coding. In Proceedings of IEEE international conference on multimedia and expo.

Daryanavard, H., Abbasi, O., & Talebi, R. (2011). FPGA implementation of JPEG-LS compression algorithm for real time applications. In Proceedings of Iranian conference on electrical engineering.

Hwang, Y.T., Lyu, M.W., & Lin, C.C. (2015). Low-complexity embedded compression codec design with rate control for high-definition video. IEEE Trans. Circuits Syst. Video Technol., 25(4), 674–687.

Kim, J., & Kyung, C.M. (2010). A lossless embedded compression using significant bit truncation for HD video coding. IEEE Trans. Circuits Syst. Video Technol., 20(6), 848–860.

Kuon, I., & Rose, J. (2007). Measuring the gap between FPGAs and ASICs. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., 26(2), 203–215.

Lee, T.Y. (2003). A new frame-recompression algorithm and its hardware design for MPEG-2 video decoders. IEEE Trans. Circuits Syst. Video Technol., 13(6), 529–534.

Li, X., Chen, X., Xie, X., Li, G., Zhang, L., Zhang, C., & Wang, Z. (2007). A low power, fully pipelined JPEG-LS encoder for lossless image compression. In Proceedings of IEEE international conference on multimedia and expo.

Papadonikolakis, M., Pantazis, V., & Kakarountas, A.P. (2007). Efficient high-performance ASIC implementation of JPEG-LS encoder. In Proceedings of design, automation & test in europe conference & exhibition (DATE) (pp. 159–164).

Son, C.H., Kim, J.W., Song, S.G., Park, S.M., & Kim, Y.M. (2010). Low complexity embedded compression algorithm for reduction of memory size and bandwidth requirements in the JPEG2000 encoder. IEEE Trans. Consum. Electron., 56(4), 2421–2429.

Tanenbaum, A.S. (1993). Computer networks. Pearson education (Singapore) pte. limited.

Tsai, T.H., & Lee, Y.H. (2010). A 6.4 Gbit/s embedded compression codec for memory-efficient applications on advanced-HD specification. IEEE Trans. Circuits Syst. Video Technol., 20(10), 1277–1291.

Walls, F., & Macinnis, A.S. (2014). 27.4 l: Late-news paper: VESA display stream compression: An overview. In SID Symposium digest of technical papers, (Vol. 45 pp. 360–363): Wiley.

Weinberger, M., Seroussi, G., & Sapiro, G. (2000). The LOCO-I lossless image compression algorithm: Principles and standardization into JPEG-LS. IEEE Trans. Images Process., 9(8), 1309–1324.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Palaz, O., Ugurdag, H.F., Ozkurt, O. et al. RImCom: Raster-order Image Compressor for Embedded Video Applications. J Sign Process Syst 88, 149–165 (2017). https://doi.org/10.1007/s11265-016-1211-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-016-1211-9