Abstract

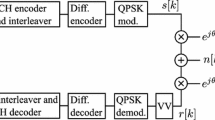

This paper presents a two-iteration concatenated Bose-Chaudhuri-Hocquenghem (BCH) code and its high-speed low-complexity two-parallel decoder architecture for 100 Gb/s optical communications. The proposed architecture features a very high data processing rate as well as excellent error correction capability. A low-complexity syndrome computation architecture and a high-speed dual-processing pipelined simplified inversonless Berlekamp-Massey (Dual-pSiBM) key equation solver architecture were applied to the proposed concatenated BCH decoder with an aim of implementing a high-speed low-complexity decoder architecture. Two-parallel processing allows the decoder to achieve a high data processing rate required for 100 Gb/s optical communication systems. Also, the proposed two-iteration concatenated BCH code structure with block interleaving methods allows the decoder to achieve 8.91dB of net coding gain performance at 10−15 decoder output bit error rate to compensate for serious transmission quality degradation. Thus, it has potential applications in next generation forward error correction schemes for 100 Gb/s optical communications.

Similar content being viewed by others

References

Berlekamp, E. R. (1968). Algebraic coding theory. New York: McGraw-Hill. revised ed.—Laguna Hills, CA: Aegean Park, 1984.

Forward Error Correction for high bit-rate DWDM Submarine System. Telecommunication Standardization Section, International Telecommunication Union, ITU-T G. 975.1, Feb. 2004.

Song, L., M-L, Yu, & Shaffer, M. S. (2002). 10 and 40-Gb/s forward error correction devices for optical communications. IEEE Journal of Solid-State Circuits, 37(11), 1565–1573.

Seki, K, Mikami, K., Katayama, A., Suzuki, S., Shinohara, N., Nakabayashi, M. (2003). Single-chip FEC codec using a concatenated BCH code for 10 Gb/s long-haul optical transmission systems. Proceedings of the 2003 IEEE Custom Integrated Circuits Conference, 279–282.

Lee, S., Choi, C.-S., & Lee, H. (2008). Two-parallel Reed-Solomon based FEC architecture for optical communications. IEICE Electronics Express (ELEX), 5(10), 374–380.

WD40. Proposed OTU4 FEC. Vitesse Semiconductor, March 2009.

WD06. Cyclically Interleaved BCH “Swizzle” FEC for OTU4 IrDI and optionally IaDI. PMC-Sierra, March 2009

WD49. Towards Optimal Trade-off for OTU4 FEC. Broadcom Corp., March, 2009

Yoon, S., Lee, H., Lee, K., Choi, C., Shin, J., Kim, J., et al. (2009) Two-parallel Concatenated BCH Super-FEC Architecture For 100-Gb/s Optical Communications. IEEE workshop on Signal Processing Systems, 36–39.

WD07. ODU4 FS Bytes. Sunnyvale, March 2009

Liu, W, Rho, J., Sung, W. (2006). Low-power high-throughput BCH error correction VLSI design for multilevel cell NAND flash memories. Proceedings of the IEEE Workshop Signal Processing Systems (SiPS): Des. Imple., pp. 248–253.

Yoon, S., Lee, H., & Lee, K. (2010). High-speed two-parallel concatenated BCH-based Super-FEC architecture for optical communications. IEICE Transactions on Fundamentals of Electronics, Communications, and Computer Sciences Systems, E92-A(4), 769–777.

Acknowledgement

This research was partly supported by the IT R&D program of the MKE/MKIT [2010-F-010-01] and partly supported by the MKE, Korea, under the ITRC support program supervised by the NIPA (NIPA-2010-C1090-1011-0007)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lee, K., Kang, HG., Park, JI. et al. A High-Speed Low-Complexity Concatenated BCH Decoder Architecture for 100 Gb/s Optical Communications. J Sign Process Syst 66, 43–55 (2012). https://doi.org/10.1007/s11265-010-0519-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-010-0519-0