Abstract

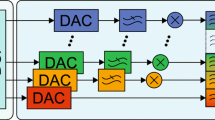

This paper addresses a problem associated with interleaved ADC systems from the digital signal processing algorithm design perspective. The output streams of an interleaved ADC system are inherently in parallel format. It would be nice if DSP algorithms can be designed to take advantage of the inherently parallel signal streams in the interleaved ADC system without the need of a high speed parallel-to-serial multiplexer. Frequency response of a parallel filter bank is derived. It is found that the overall frequency response is the average of each individual interpolated channel filter plus the aliasing components. The aliasing components come from the deviation of each individual channel from the average response.

Results are applied to characterize the gain mismatch of ADC arrays. Sinusoidal response is also investigated. The results can be used to characterize the frequency response mismatch of ADC arrays.

Similar content being viewed by others

References

W.C. Black and D.A Hodges, “Time Interleaved Converter Arrays,” IEEE Journals on Solid State Circuits, vol. SC-15, no. 6, 1980.

K. Poulton, J.J. Corcoran, and T. Hornac, “A 1-GHz 6-bitTime ADC System,” IEEE Journals on Solid State Circuits, vol. SC-22, no. 6, 1987.

Y.C. Jenq, “Digital Spectra of Non-Uniformly Sampled Signals: A Robust Sampling Time Offset Estimation Algorithm for Ultra High-Speed Waveform Digitizers Using Interleaving,” IEEE Transactions on Instrumentation and Measurement, vol. IM-39, no. 1, 1990.

A. Petraglia and S.K. Mitra, “Analysis of Mismatch Effects Among A/D Converters in a Time-Interleaved Waveform Digitizer,” IEEE Transactions on Instrumentation and Measurement, vol. IM-40, no. 5, 1991.

Y.C. Jenq, “Perfect Reconstruction of Digital Spectrum from Non-Uniformly Sampled Signals,” IEEE Transactions on Instrumentation and Measurement, vol. IM-46, no. 3, 1997.

H. Jin and K.F. Lee, “A Digital-Background Calibration Technique for Minimizing Time-Error Effects in Time-Interleaved ADC’s,” IEEE Transactions on Circuits and Systems II, vol. 47, no. 7, 2000.

H. Johansson and P. Lowenborg, “Reconstruction of Non-Uniformly Sampled Bandlimited Signals Using Digital Fractional Delay Filters,” in Proceedings of IEEE International Symposium on Circuits and Systems, Sidney, Australia, May 2001.

P.P. Vaidyanathan, Multirate Systems and Filter Banks, Englewood Cliffs, NJ: Prentice Hall, 1993.

Author information

Authors and Affiliations

Corresponding author

Additional information

Yih-Chyun Jenq received the B.S.E. degree from National Taiwan University, Taipei, Taiwan in 1971, and the M.S.E., M.A., and Ph.D. degrees in Electrical Engineering from Princeton University, Princeton, NJ in 1974, 1975, and 1976, respectively. From 1976 to 1980, he was Assistant Professor of Electrical Engineering at the State University of New York at Stony Brook, Stony Brook, NY. From 1980 to 1984, he was a Member of Technical Staff at AT&T Bell Laboratories, Homdel, NJ. From 1984 to 1990, he was a Research Manager and Principal Engineer at Tektronix Laboratories, Beaverton, OR. In September 1990, he joined the Faculty of the Department of Electrical and Computer Engineering at Portland State University, Portland, OR where he is currently a Full Professor. From 1987 to 1989, Dr. Jenq served as Associate Editor of the IEEE Transactions on Circuits and Systems in charge of Digital Signal Processing. He was the recipient of the 1988 Andrew R. Chi Prize Paper Award of the IEEE Instrumentation and Measurement Society. He holds ten (10) U.S. patents. Dr. Jenq is a fellow of the IEEE.

Rights and permissions

About this article

Cite this article

Jenq, YC. Digital Signal Processing with Interleaved ADC Systems. J VLSI Sign Process Syst Sign Image Video Technol 39, 267–271 (2005). https://doi.org/10.1007/s11265-005-4844-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-005-4844-7