Abstract

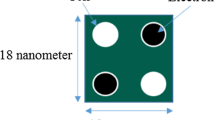

Features like ultra-dense structure and ultra-low power consumption of the quantum-dot cellular automata (QCA) have made this nanotechnology a viable alternative to complementary metal–oxide–semiconductor (CMOS) technology. The arithmetic logic unit (ALU) is the fundamental and inseparable part of each processor. This paper presented a new reversible ALU which is made up of three Modified Fredkin (MF) gates and a novel coplanar reversible full adder relying on the HNG gate in QCA nanotechnology. This structure consists of 350 QCA cells are arranged in a 0.411 μm2 area and is implemented using the coplanar clock-zone-based crossover. Also, this layout can execute 20 distinctive arithmetic and logic functions, and its outputs are produced in three clock cycles (12 clock phases). The QCA implementation of the proposed structure is simulated and evaluated by QCADesigner version 2.0.3. Simulation outcomes authenticate that the proposed QCA reversible ALU has a 60.62%, 38.47%, 27.08%, 20%, and 14.28% amelioration in QCA cost, area occupancy, cell count, latency, and quantum cost, respectively, compared to the prior best coplanar structure.

Similar content being viewed by others

References

Abdullah-Al-Shafi, M., Bahar, A.N., Habib, M.A., Bhuiyan, M.M.R., Ahmad, F., Ahmad, P.Z., Ahmed, K.: Designing single layer counter in quantum-dot cellular automata with energy dissipation analysis. Ain Shams Eng. J. 9(4), 2641–2648 (2018)

Adelnia, Y., Rezai, A.: A novel adder circuit design in quantum-dot cellular automata technology. Int. J. Theor. Phys. 58(1), 184–200 (2019)

Ahmad, F., Ahmed, S., Kakkar, V., Bhat, G.M., Bahar, A.N., Wani, S.: Modular design of ultra-efficient reversible full adder-subtractor in QCA with power dissipation analysis. Int. J. Theor. Phys. 57(9), 2863–2880 (2018)

Ahmadpour, S.-S., Mosleh, M.: New designs of fault-tolerant adders in quantum-dot cellular automata. Nano Commun. Networks 19, 10–25 (2019)

Ahmadpour, S.-S., Mosleh, M., Heikalabad, S.R.: A revolution in nanostructure designs by proposing a novel QCA full-adder based on optimized 3-input XOR. Physica B 550, 383–392 (2018)

Ahmadpour, S.S., Mosleh, M., Rasouli Heikalabad, S.: Robust QCA full-adders using an efficient fault-tolerant five-input majority gate. Int. J. Circuit Theory Appl. 47(7), 1037–1056 (2019)

Ahmed, S., Baba, M.I., Bhat, S.M., Manzoor, I., Nafees, N., Ko, S.-B.: Design of reversible universal and multifunctional gate-based 1-bit full adder and full subtractor in quantum-dot cellular automata nanocomputing. J. Nanophotonics 14(3), 036002 (2020)

Angizi, S., Alkaldy, E., Bagherzadeh, N., Navi, K.: Novel robust single layer wire crossing approach for exclusive or sum of products logic design with quantum-dot cellular automata. J. Low Power Electron. 10(2), 259–271 (2014)

Asfestani, M.N., Heikalabad, S.R.: A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Physica B 512, 91–99 (2017)

Barenco, A., Bennett, C.H., Cleve, R., DiVincenzo, D.P., Margolus, N., Shor, P., Sleator, T., Smolin, J.A., Weinfurter, H.: Elementary gates for quantum computation. Phys. Rev. A 52(5), 3457 (1995)

Barughi, Y.Z., Heikalabad, S.R.: A three-layer full adder/subtractor structure in quantum-dot cellular automata. Int. J. Theor. Phys. 56(9), 2848–2858 (2017)

Bennett, C.H.: Logical reversibility of computation. IBM J. Res. Dev. 17(6), 525–532 (1973)

Bhat, S.M., Ahmed, S.: Design of ultra-efficient reversible gate based 1-bit full adder in QCA with power dissipation analysis. Int. J. Theor. Phys. 58(12), 4042–4063 (2019)

Bhuvana, B.P., Kanchana Bhaaskaran, V.S.: Quantum cost optimization of reversible adder/subtractor using a novel reversible gate. In: Innovations in electronics and communication engineering, pp. 111–118. Springer, Singapore (2018)

Bilal, B., Ahmed, S., Kakkar, V.: Modular adder designs using optimal reversible and fault tolerant gates in field-coupled QCA nanocomputing. Int. J. Theor. Phys. 57(5), 1356–1375 (2018)

Chaves, J. F., Silva, D. S., Camargos, V. V., & Neto, O. P. V.: Towards reversible QCA computers: reversible gates and ALU. Paper presented at the 2015 IEEE 6th Latin American symposium on circuits & systems (LASCAS), (2015)

Feynman, R.P.: Quantum mechanical computers. Found. Phys. 16(6), 507–531 (1986)

Fredkin, E., Toffoli, T.: Conservative logic. Int. J. Theor. Phys. 21(3), 219–253 (1982)

Goswami, M., Sen, B., Mukherjee, R., Sikdar, B.K.: Design of testable adder in quantum-dot cellular automata with fault secure logic. Microelectron. J. 60, 1–12 (2017)

Gupta, A., Malviya, U., & Kapse, V.: Design of speed, energy and power efficient reversible logic based vedic ALU for digital processors. Paper presented at the 2012 Nirma university international conference on engineering (NUiCONE), (2012)

Haghparast, M., Navi, K.: A novel reversible BCD adder for nanotechnology based systems. Am. J. Appl. Sci. 5(3), 282–288 (2008)

Hashemi, S., Azghadi, M.R., Navi, K.: Design and analysis of efficient QCA reversible adders. J. Supercomput. 75(4), 2106–2125 (2019)

Hashemi, S., Tehrani, M., Navi, K.: An efficient quantum-dot cellular automata full-adder. Sci. Res. Essays 7(2), 177–189 (2012)

Heikalabad, S.R.: Non-coplanar counter in quantum-dot cellular automata. Eur. Phys. J. Plus 136(2), 209 (2021). https://doi.org/10.1140/epjp/s13360-021-01198-1

Heikalabad, S.R., Kamrani, H.: Design and implementation of circuit-switched network based on nanoscale quantum-dot cellular automata. Photonic Netw. Commun. 38(3), 356–377 (2019). https://doi.org/10.1007/s11107-019-00864-w

Heikalabad, S.R., Asfestani, M.N., Hosseinzadeh, M.: A full adder structure without cross-wiring in quantum-dot cellular automata with energy dissipation analysis. J. Supercomput. 74(5), 1994–2005 (2018)

Heikalabad, S.R., Salimzadeh, F., Barughi, Y.Z.: A unique three-layer full adder in quantum-dot cellular automata. Comput. Electr. Eng. 86, 106735 (2020). https://doi.org/10.1016/j.compeleceng.2020.106735

Heikalabad, S.R., Ahmadi, R., Salimzadeh, F.: Introducing a full-adder structure for finite field in QCA. ECS J. Solid State Sci. Technol. 10(6), 063006 (2021). https://doi.org/10.1149/2162-8777/ac08d9

Hosseinzadeh, H., Heikalabad, S.R.: A novel fault tolerant majority gate in quantum-dot cellular automata to create a revolution in design of fault tolerant nanostructures, with physical verification. Microelectron. Eng. 192, 52–60 (2018)

Kamaraj, A., Marichamy, P.: Design of fault-tolerant reversible floating point division. Informacije MIDEM 48(3), 161–172 (2018)

Kamaraj, A., Marichamy, P.: Design of integrated reversible fault-tolerant arithmetic and logic unit. Microprocess. Microsyst. 69, 16–23 (2019)

Kamrani, H., Heikalabad, S.R.: Design and implementation of multiplication algorithm in quantum-dot cellular automata with energy dissipation analysis. J. Supercomput. 77(6), 5779–5805 (2021). https://doi.org/10.1007/s11227-020-03478-6

Knill, E., Laflamme, R., Milburn, G.J.: A scheme for efficient quantum computation with linear optics. nature 409(6816), 46–52 (2001)

Kumar, P., Singh, S.: Optimization of the area efficiency and robustness of a QCA-based reversible full adder. J. Comput. Electron. 18(4), 1478–1489 (2019)

Kunalan, D., Cheong, C. L., Chau, C. F., & Ghazali, A. B.: Design of a 4-bit adder using reversible logic in quantum-dot cellular automata (QCA). Paper presented at the 2014 IEEE international conference on semiconductor electronics (ICSE2014) (2014)

Labrado, C., Thapliyal, H.: Design of adder and subtractor circuits in majority logic-based field-coupled QCA nanocomputing. Electron. Lett. 52(6), 464–466 (2016)

Landauer, R.: Irreversibility and heat generation in the computing process. IBM J. Res. Dev. 5(3), 183–191 (1961)

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology 4(1), 49–57 (1993a)

Lent, C.S., Tougaw, P.D., Porod, W.: Bistable saturation in coupled quantum dots for quantum cellular automata. Appl. Phys. Lett. 62(7), 714–716 (1993b)

Ma, X.: Physical/biochemical inspired computing models for reliable nano-technology systems: Citeseer. (2008)

Maharaj, J., Muthurathinam, S.: Effective RCA design using quantum dot cellular automata. Microprocess. Microsyst. 73, 102964 (2020)

Mano, M. M.: Computer system architecture (Vol. 3): Prentice Hall Englewood Cliffs (1993)

Miller, D. M., Wille, R., & Drechsler, R.: Reducing reversible circuit cost by adding lines. Paper presented at the 2010 40th IEEE international symposium on multiple-valued logic (2010)

Mohammadi, M., Eshghi, M.: On figures of merit in reversible and quantum logic designs. Quantum Inf. Process. 8(4), 297–318 (2009)

Mohammadi, Z., Mohammadi, M.: Implementing a one-bit reversible full adder using quantum-dot cellular automata. Quantum Inf. Process. 13(9), 2127–2147 (2014)

Mosleh, M.: A novel full adder/subtractor in quantum-dot cellular automata. Int. J. Theor. Phys. 58(1), 221–246 (2019)

Naghibzadeh, A., Houshmand, M.: Design and simulation of a reversible ALU by using QCA cells with the aim of improving evaluation parameters. J. Comput. Electron. 16(3), 883–895 (2017)

Navi, K., Sayedsalehi, S., Farazkish, R., Azghadi, M.R.: Five-input majority gate, a new device for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 7(8), 1546–1553 (2010a)

Navi, K., Farazkish, R., Sayedsalehi, S., Azghadi, M.R.: A new quantum-dot cellular automata full-adder. Microelectron. J. 41(12), 820–826 (2010b)

Norouzi, A., Heikalabad, S.R.: Design of reversible parity generator and checker for the implementation of nano-communication systems in quantum-dot cellular automata. Photonic Netw. Commun. 38(2), 231–243 (2019). https://doi.org/10.1007/s11107-019-00850-2

Norouzi, M., Heikalabad, S.R., Salimzadeh, F.: A reversible ALU using HNG and Ferdkin gates in QCA nanotechnology. Int. J. Circuit Theory Appl. 48(8), 1291–1303 (2020)

Oskouei, S.M., Ghaffari, A.: Designing a new reversible ALU by QCA for reducing occupation area. J. Supercomput. 75(8), 5118–5144 (2019)

Parhami, B.: Fault-tolerant reversible circuits. Paper presented at the 2006 fortieth asilomar conference on signals, systems and computers (2006)

Peres, A.: Reversible logic and quantum computers. Phys. Rev. A 32(6), 3266 (1985)

Perri, S., Corsonello, P., Cocorullo, G.: Area-delay efficient binary adders in QCA. IEEE Trans. Integr. (VLSI) Syst. 22(5), 1174–1179 (2013)

Roohi, A., DeMara, R.F., Khoshavi, N.: Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46(6), 531–542 (2015)

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., Navi, K.: A symmetric quantum-dot cellular automata design for 5-input majority gate. J. Comput. Electron. 13(3), 701–708 (2014)

Safoev, N., Jeon, J.-C.: A novel controllable inverter and adder/subtractor in quantum-dot cellular automata using cell interaction based XOR gate. Microelectron. Eng. 222, 111197 (2020)

Salimzadeh, F., Heikalabad, S.R.: A full adder structure with a unique XNOR gate based on Coulomb interaction in QCA nanotechnology. Opt. Quantum Electron. 53(8), 479 (2021). https://doi.org/10.1007/s11082-021-03127-z

Salimzadeh, F., Heikalabad, S.R., Gharehchopogh, F.S.: Design of a reversible structure for memory in quantum-dot cellular automata. Int. J. Circuit Theory Appl. 48(12), 2257–2265 (2020). https://doi.org/10.1002/cta.2807

Salimzadeh, F., Safarpoor, E., Heikalabad, S.R.: Designing and implementing a fault-tolerant priority encoder in QCA nanotechnology. ECS J. Solid State Sci. Technol. 10(6), 063004 (2021). https://doi.org/10.1149/2162-8777/ac0118

Sasamal, T.N., Singh, A.K., Mohan, A.: Efficient design of reversible alu in quantum-dot cellular automata. Optik 127(15), 6172–6182 (2016)

Sasamal, T.N., Singh, A.K., Mohan, A.: Design of cost-efficient qca reversible circuits via clock-zone-based crossover. Int. J. Theor. Phys. 57(10), 3127–3140 (2018a)

Sasamal, T.N., Mohan, A., Singh, A.K.: Efficient design of reversible logic ALU using coplanar quantum-dot cellular automata. J. Circuits, Syst. Comput. 27(02), 1850021 (2018b)

Sasamal, T.N., Singh, A.K., Mohan, A.: An efficient design of quantum-dot cellular automata based 5-input majority gate with power analysis. Microprocess. Microsyst. 59, 103–117 (2018c)

Sen, B., Dutta, M., Goswami, M., Sikdar, B.K.: Modular design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelectron. J. 45(11), 1522–1532 (2014)

Seyedi, S., Navimipour, N.J.: An optimized design of full adder based on nanoscale quantum-dot cellular automata. Optik 158, 243–256 (2018)

Singh, S., Choudhary, A., Jain, M.K.: A brief overview of reversible logic gate and reversible circuits. Int J Electron Eng 11(2), 86–104 (2019)

Singh, P., Majumder, A., Chowdhury, B., Mondal, A., Shekhawat, T.: Reducing delay and quantum cost in the novel design of reversible memory elements. Proced. Comput. Sci. 57, 189–198 (2015)

Taherkhani, E., Moaiyeri, M.H., Angizi, S.: Design of an ultra-efficient reversible full adder-subtractor in quantum-dot cellular automata. Optik 142, 557–563 (2017)

Toffoli, T.: Reversible computing. Paper presented at the international colloquium on automata, languages, and programming (1980)

Tougaw, P.D., Lent, C.S.: Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75(3), 1818–1825 (1994)

Tougaw, P.D., Lent, C.S., Porod, W.: Bistable saturation in coupled quantum-dot cells. J. Appl. Phys. 74(5), 3558–3566 (1993)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Wille, R., Soeken, M., Miller, D.M., Drechsler, R.: Trading off circuit lines and gate costs in the synthesis of reversible logic. Integration 47(2), 284–294 (2014)

Zhang, Y., Xie, G., Sun, M., Lv, H.: An efficient module for full adders in quantum-dot cellular automata. Int. J. Theor. Phys. 57(10), 3005–3025 (2018)

Funding

The authors have not disclosed any funding.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have not disclosed any competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Aliabadian, R., Golsorkhtabaramiri, M., Heikalabad, S.R. et al. Design of a reversible ALU using a novel coplanar reversible full adder and MF gate in QCA nanotechnology. Opt Quant Electron 55, 191 (2023). https://doi.org/10.1007/s11082-022-04382-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11082-022-04382-4