Abstract

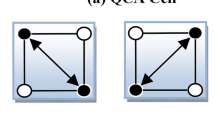

Quantum-dot cellular automata (QCA) is one of the most attractive alternatives for complementary metal-oxide semiconductor technology. The QCA widely supports a new paradigm in the field of nanotechnology that has the potential for high density, low power, and high speed. The clock manager is an essential building block in the new microwave and radio frequency integrated circuits. This paper describes a novel QCA-based clock management unit (CMU) that provides innovative clocking capabilities. The proposed CMU is achieved by utilizing edge-triggered D-type flip-flops (D-FFs) in the design of frequency synthesizer and phase splitter. Edge-triggered D-FF structures proposed in this paper have the successful QCA implementation and simulation with the least complexity and power dissipation as compared to earlier structures. The frequency synthesizer is used to generate new clock frequencies from the reference clock frequency based on a combination of power-of-two frequency dividers. The phase splitter is integrated with the frequency synthesizer to generate four clock signals that are 90o out of phase with each other. This paper demonstrates that the proposed QCA CMU structure has a superior performance. Furthermore, the proposed CMU is straightforwardly scalable due to the use of modular component architecture.

Similar content being viewed by others

References

Angizi S, Navi K, Sayedsalehi S, Navin AH (2014) Efficient quantum dot cellular automata memory architectures based on the new wiring approach. J Comput Theor Nanosci 11:2318–2328

D.A. Antonelli, D.Z. Chen, T.J. Dysart, X.S. Hu, A.B. Kahng, P.M. Kogge, R.C. Murphy, M.T. Niemier (2004) Quantum-dot cellular automata (QCA) circuit partitioning: problem modeling and solutions. The 41st Design Automation Conference (DAC), pp. 363–368

Blair EP, Yost E, Lent CS (2009) Power dissipation in clocking wires for clocked molecular quantum-dot cellular automata. J Comput Electron 9:49–55

Cho H, Swartzlander EE Jr (2009) Adder and multiplier design in quantum-dot cellular automata. IEEE Trans Comput 58:721–727

Coussy P, Morawiec A (2008) High-level synthesis: from algorithm to digital circuit. Springer, Berlin

Dehkordi MA, Shamsabadi AS, Ghahfarokhi BS, Vafaei A (2011) Novel RAM cell designs based on inherent capabilities of quantum-dot cellular automata. Microelectron J 42:701–708

Dysart TJ (2013) Modeling of electrostatic QCA wires. IEEE Trans Nanotechnol 12:553–560

S.E. Frost, A.F. Rodrigues, A.W. Janiszewski, R.T. Rausch, P.M. Kogge 2002, Memory in motion: a study of storage structures in QCA, First Workshop on Non-silicon Computing

Hashemi S, Navi K (2012) New robust QCA D flip flop and memory structures. Microelectron J 43:929–940

Hu W, Sarveswaran K, Lieberman M, Bernstein GH (2005) High-resolution electron beam lithography and DNA nano-patterning for molecular QCA. IEEE Trans Nanotechnol 4:312–316

Huang J, Momenzadeh M, Lombardi F (2007) Design of sequential circuits by quantum dot cellular automata. Microelectron J 38:525–537

Khatun M, Padgett B, Anduwan G, Sturzu I, Tougaw D (2013) Defect and temperature effects on complex quantum-dot cellular automata devices. Journal of Applied Mathematics and Physics 1:7–15

Kim K, Wu K, Karri R (2006) Quantum-dot cellular automata design guideline. IEICE Trans Fundam Electron Commun Comput Sci 89:1607–1614

Lent CS, Tougaw PD (1997) A device architecture for computing with quantum dots. Proc IEEE 85:541–557

Lent CS, Tougaw PD, Porod W, Bernstein GH (1993) Quantum cellular automata. Nanotechnology 4:49–57

Lent CS, Liu M, Lu Y (2006) Bennett clocking of quantum dot cellular automata and the limits to binary logic scaling. Nanotechnology 17(16):4240–4251

Liu W, Lu L, O’Neill M, Swartzlander EE Jr (2011) Design rules for quantum-dot cellular automata. Proc IEEE Int Symp Circuits Syst:2361–2364

Liu W, Swartzlander EE Jr, O’Neill M (2013) Design of semiconductor QCA systems. Artech House, USA

Lu Y, Lent CS (2005) Theoretical study of molecular quantum-dot cellular automata. J Comput Electron 5:115–118

Lu Y, Liu M, Lent C (2007) Molecular quantum-dot cellular automata: from molecular structure. J Appl Phys 102:034311–034317

Mandal D, Bhattacharyya TK (2008) Implementation of CMOS low-power integer-N frequency synthesizer for SOC design. J Comput Secur 3(4):31–38

Ravichandran R, Lim SK, Niemier M (2005) Automatic cell placement for quantum-dot cellular automata. Integr VLSI J 38:541–548

Razavi B, Lee KF, Yan RH (1995) Design of high-speed, low-power frequency dividers and phase-locked loops in deep submicron CMOS. IEEE J Solid State Circuits 30(2):101–109

Safarian A, Anand S, Heydari P (2006) On the dynamics of regenerative frequency dividers. IEEE Trans Circuits Syst II, Express Briefs 53:1413–1417

K. Sengupta, H. Hashemi (2006) Maximum frequency of operation of CMOS static frequency dividers: theory and design techniques. 13th IEEE International Conference on Electronics, Circuits AND Systems (ICECS ‘2006), pp. 584–587

Shamsabadi AS, Ghahfarokhi BS, Zamanifar K, Vafaei A (2009) Applying inherent capabilities of quantum-dot cellular automata to design: D flip-flop case study. J Syst Archit 55:180–187

Sheikhfaal S, Angizi S, Sarmadi S, Moaiyeri MH, Sayedsalehi S (2015) Designing efficient QCA logical circuits with power dissipation analysis. Microelectron J 46:462–471

Shu K, Snchez-Sinencio E (2004) CMOS PLL synthesizers: analysis and design. Springer, Berlin

Srivastava S, Sarkar S, Bhanja S (2009) Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans Nanotechnol 8:116–127

Srivastava S, Asthana A, Bhanja S, Sarkar S (May 2011) QCAPro-an error power estimation tool for QCA circuit design. Proc. IEEE Int. Symp. Circuits Syst.:2377–2380

Taskin B, Hong B (2008) Improving line-based QCA memory cell design through dual phase clocking. IEEE Trans Very Large Scale Integration (VLSI) Syst 16:1648–1656

Timler J, Lent CS (2002) Power gain and dissipation in quantum dot cellular automata. J Appl Phys 91:823–830

Vankamamidi V, Ottavi M, Lombardi F (2005) A line-based parallel memory for QCA implementation. IEEE Trans Nanotechnol 4:690–698

Vankamamidi V, Ottavi M, Lombardi F (2008) A serial memory by quantum-dot cellular automata (QCA). IEEE Trans Comput 57:606–618

Vetteth A, Walus K, Dimitrov VS, Jullien GA (2003) Quantum-dot cellular automata of flip-flops. ATIPS Laboratory 2500 University Drive, Alberta

Walus K, Dysart TJ, Jullien GA, Budiman RA (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3:26–31

Xiao L, Chen X, Ying S (2012) Design of dual-edge triggered flip-flops based on quantum-dot cellular automata. Journal of Zhejiang University SCIENCE C 13(5):385–392

K.K. Yadavalli, A.O. Orlov, K. Kummamuru, C.S. Lent, G.H. Bernstein, G.L. Snider (2006) Fanout in quantum dot cellular automata, 63rd Device Research Conference Digest (DRC ‘05), Santa Barbara, CA, pp. 121–122

Yang X, Cai L, Zhao X (2010) Low power dual-edge triggered flip-flop structure in quantum dot cellular automata. Electron Lett 46:825–626

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Rights and permissions

About this article

Cite this article

Abutaleb, M.M. A novel power-efficient high-speed clock management unit using quantum-dot cellular automata. J Nanopart Res 19, 128 (2017). https://doi.org/10.1007/s11051-017-3810-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11051-017-3810-1