Abstract

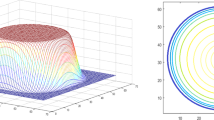

This paper presents a low complexity two dimensional (2D) circular symmetric Finite Impulse Response (FIR) filter design and implementation of architecture. The optimized circular symmetric 2D FIR filter is designed using a modified Park–McClellan transformation method and filter coefficients are quantized using a canonical signed digit (CSD) binary number format. The CSD encoded coefficients are optimized to reduce the number of adder/subtractors using common subexpression elimination (CSE) algorithms. Based on the modified filter coefficients, the two structures fully direct form and hybrid-II form 2D FIR filter architectures are implemented using CSD and CSD with Horizontal CSE and Vertical CSE techniques. The proposed architectures compared with the conventional symmetry 2D filters and state-of-the-art architectures in terms of area, power, and speed.

Similar content being viewed by others

References

Aksoy, L., Flores, P., & Monteiro, J. (2014). A tutorial on multiplierless design of FIR filters: Algorithms and architectures. Circuits, Systems, and Signal Processing, 33(6), 1689–1719.

Baboji, K., & Sridevi, S. (2019). Optimal design of multiplier-less non-uniform channel filters with successive approximation of vectors. Circuits, Systems, and Signal Processing, 1–24.

Bindima, T., & Elias, E. (2016). Design of efficient circularly symmetric two-dimensional variable digital FIR filters. Journal of Advanced Research, 7(3), 336–347.

Bindima, T., & Elias, E. (2017). Design and implementation of low complexity 2-D variable digital FIR filters using single-parameter-tunable 2-D farrow structure. IEEE Transactions on Circuits and Systems I: Regular Papers, 65(2), 618–627.

Bindima, T., & Elias, E. (2019). Low-complexity 2-D digital FIR filters using polyphase decomposition and farrow structure. IEEE Transactions on Circuits and Systems I: Regular Papers, 66(6), 2298–2308.

Bindima, T., Manuel, M., & Elias, E. (2016). An efficient transformation for two dimensional circularly symmetric wideband FIR filters. 2016 IEEE Region 10 Conference (TENCON). IEEE.

Chandra, A., & Chattopadhyay, S. (2016). A new strategy of image denoising using multiplier-less FIR filter designed with the aid of the differential evolution algorithm. Multimedia Tools and Applications, 75(2), 1079–1098.

Chen, P. Y., Van, L. D., Khoo, I. H., Reddy, H. C., & Lin, C. T. (2010). Power-efficient and cost-effective 2-D symmetry filter architectures. IEEE Transactions on Circuits and Systems I: Regular Papers, 58(1), 112–125.

Chen, P. Y., Van, L. D., Reddy, H. C., & Khoo, I. H. (2013). Area-efficient 2-D digital filter architectures possessing diagonal and four-fold rotational symmetries. In: 2013 9th International Conference on Information, Communications & Signal Processing (IEEE) (pp. 1–5).

Das, P., Naskar, S. K., & Narayan Patra, S. (2019). Fast converging cuckoo search algorithm to design symmetric FIR filters. International Journal of Computers and Applications, 1–19.

Dwivedi, A. K., Ghosh, S., & Londhe, N. D. (2016). Low power 2D finite impulse response filter design using modified artificial bee colony algorithm with experimental validation using field-programmable gate array. IET Science, Measurement and Technology, 10(6), 671–678.

Guo, R., & DeBrunner, L. S. (2011). Two high-performance adaptive filter implementation schemes using distributed arithmetic. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(9), 600–604.

Hsiao, S.-F., Jian, J.-H. Z., & Chen, M.-C. (2013). Low-cost FIR filter designs based on faithfully rounded truncated multiple constant multiplication/accumulation. IEEE Transactions on Circuits and Systems II: Express Briefs, 60(5), 287–291.

Khoo, I. H., Reddy, H. C., Van, L. D., & Lin, C. T. (2010). Generalized formulation of 2-D filter structures without global broadcast for VLSI implementation. In: 2010 53rd IEEE international Midwest symposium on circuits and systems (pp. 426–429). IEEE.

Kumar, P., Shrivastava, P. C., Tiwari, M., & Dhawan, A. (2018). ASIC Implementation of area-efficient, high-throughput 2-D IIR filter using distributed arithmetic. Circuits, Systems, and Signal Processing, 37(7), 2934–2957.

Kumar, P., Shrivastava, P. C., Tiwari, M., & Mishra, G. R. (2019). High-throughput, area-efficient architecture of 2-D block FIR filter using distributed arithmetic algorithm. Circuits, Systems, and Signal Processing, 38(3), 1099–1113.

Liu, J.-C., & Tai, Y.-L. (2010). Design of 2-D wideband circularly symmetric FIR filters by multiplierless high-order transformation. IEEE Transactions on Circuits and Systems I: Regular Papers, 58(4), 746–754.

Meher, P. K., & Park, S. Y. (2011). High-throughput pipelined realization of adaptive FIR filter based on distributed arithmetic. VLSI Symp. Tech. Dig., 428–433.

Mohanty, B. K., Meher, P. K., Al-Maadeed, S., & Amira, A. (2013). Memory footprint reduction for power-efficient realization of 2-D finite impulse response filters. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(1), 120–133.

Odugu, V. K., Venkata Narasimhulu, C., & Prasad, K. S. (2019). Implementation of low power and memory efficient 2D FIR filter architecture. International Journal of Recent Technology and Engineering, 8(1), 927–935.

Parhi, K. K. (1999). VLSI digital signal processing systems. New York, USA: Wiley.

Shyu, J.-J., Pei, S.-C., & Huang, Y.-D. (2008). Design of variable two-dimensional FIR digital filters by McClellan transformation. IEEE Transactions on Circuits and Systems I: Regular Papers, 56(3), 574–582.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Odugu, V.K., Venkata Narasimhulu, C. & Satya Prasad, K. Design and implementation of low complexity circularly symmetric 2D FIR filter architectures. Multidim Syst Sign Process 31, 1385–1410 (2020). https://doi.org/10.1007/s11045-020-00714-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11045-020-00714-3